Shimon P. Vingron

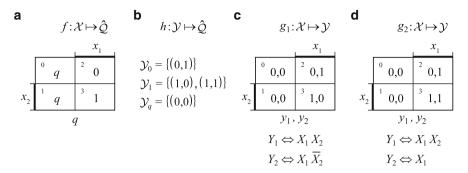

# Logic Circuit Design

Selected Methods

### Logic Circuit Design

Shimon P. Vingron

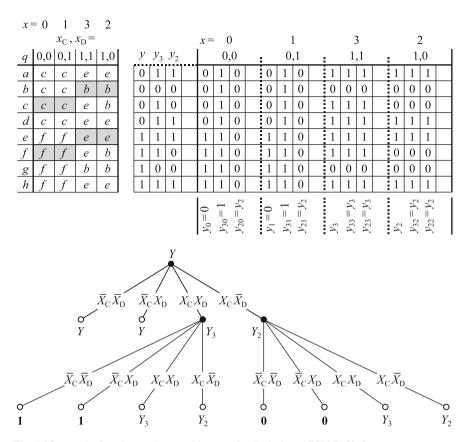

## Logic Circuit Design

Selected Methods

Shimon P. Vingron Bärenkogelweg 21 2371 Hinterbrühl Austria

ISBN 978-3-642-27656-9 e-ISBN 978-3-642-27657-6 DOI 10.1007/978-3-642-27657-6 Springer Heidelberg Dordrecht London New York

Library of Congress Control Number: 2012935652

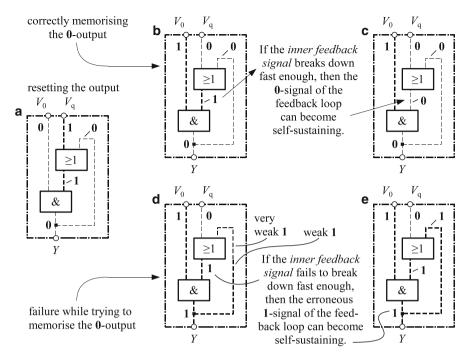

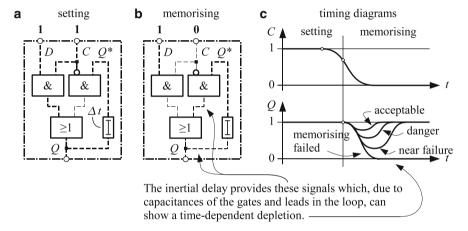

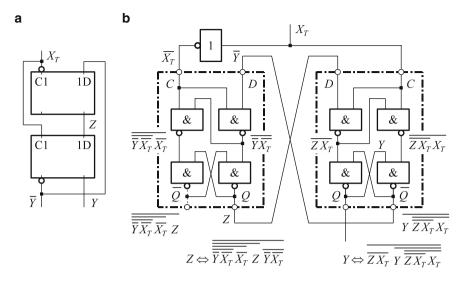

© Springer-Verlag Berlin Heidelberg 2012

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilm or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer. Violations are liable to prosecution under the German Copyright Law.

The use of general descriptive names, registered names, trademarks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

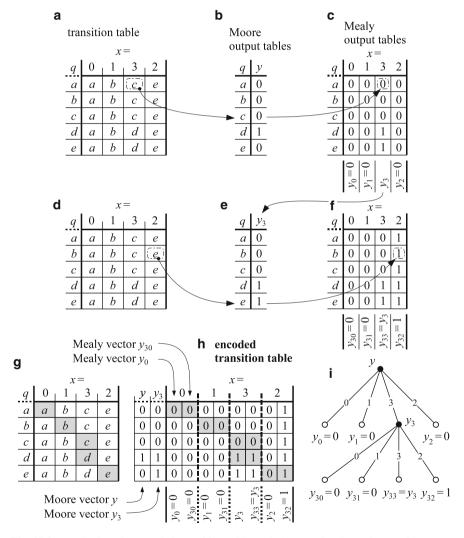

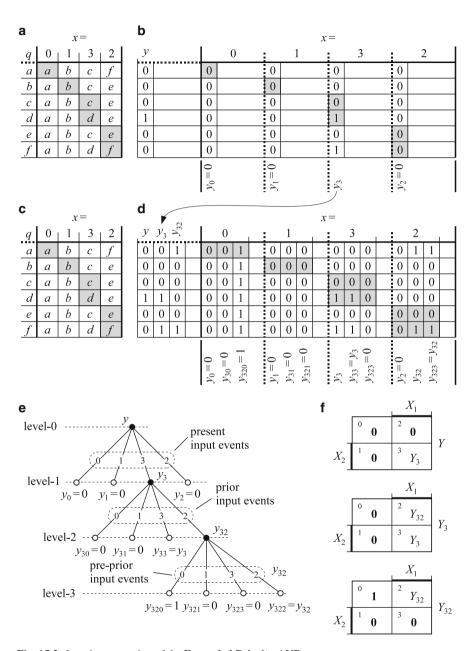

For my wife, Dora, the spirit of the family, the companion and love of my life.

#### **Preface**

This book introduces you to the **design of logic circuits**. In these times of the scientific journal it has become customary for a scientific book, in the main, to contain well-established knowledge while new findings are presented in scientific journals, preferably ones peer reviewed. As J.R.R. Tolkien says of his Hobbits in the prologue to 'The Fellowship of the Ring', '... they liked to have books filled with things that they already knew, set out fair and square with no contradictions'. But this is not a Hobbitian book: While I certainly have tried to set things out fairly and squarely and hope to have avoided contradictions, major parts of this book contain new findings. These, when put together and presented in context, draw a totally new picture of sequential circuits. As the whole is more than just the sum of its parts, I thought it advisable to give a picture as complete as possible, thus the book form, and not to split the material into small parts adequate for journals, but lacking in meaning if not seen in context.

The subject matter is divided into three divisions, the first covering circuits that have no memorising ability, the **combinational circuits**, the second presents pure memory circuits, the **latches**, the third investigates circuits which have a memorising ability to various degrees, the **sequential circuits**. The presentation is not theoretical, in that most proofs have been omitted, hopefully making the text more readable. But there is still enough algebraic content to warrant using paper and pencil parallel to reading the book.

**Part I**, on **Combinational Circuits**, draws completely upon the first three divisions of Vingron (2004); their approximately 260 pages have not only been excerpted to the present 95, but a number of improvements have been put in place (Sects. 1.1–1.3, and 2.2, Chaps. 5, 6, and 8). Especially Chap. 8, on the composition of combinational circuits, points to a new and important design technique. With a heavy heart I have refrained from all proofs in connection with normal forms (Chap. 4) and have omitted chapters on *nand* and *nor* design techniques, and on *hazards*. Combinational circuits are quite easily recognised as being describable by the laws of logic. In a rather roundabout way this insight was first achieved by analysing circuits built of electric relays, but is, of course, independent of the technology by which a circuit is realised.

viii Preface

**Part II** is on **Latches**, these being the elementary form of sequential circuits, and allowing us to study memorisation in its most basic form. Memorisation is conventionally taken to be a time-dependent phenomenon, a notion that has always stood in the way of describing latches (and subsequently sequential circuits) by the the laws of logic (as was so successfully done for combinational circuits). The major achievement, presented in Chap. 9, is to find a time-*independent* description of memory making it possible to use logic in its conventional form (not, temporal logic) in working with latches. Despite a superfluous similarity with the division on latches of Vingron (2004), the present division on latches has been completely reworked and rewritten (especially Chaps. 9 and 10) putting the theory of latches on a new footing.

Part III is on asynchronous sequential circuits. Their theory was initiated by Huffman (1954) landmark paper 'The Synthesis of Sequential Switching Circuits'. In this wonderfully readable paper (no maths!) he actually didn't present a theory—he put forth verbally expressed procedures saying how to develop asynchronous circuits. His presentation and arguments were so persuasive that all subsequent theory (it came to be known as automata theory) seemed to be focussed on providing a mathematical background and justification. The quantized time-dependent mathematical models that automata theory developed led to the introduction of synchronous sequential circuits. They are usually explained as being clock driven meaning that all switching activity takes place during brief and periodically recurring time intervals. Asynchronous circuits (Huffman's original sequential circuits) are not clocked. They employ continuously present signals, and the outputs can change whenever an input changes. Automata theory had practically no success in advancing the theory of asynchronous circuits.

Part III breaks with the standard synthesis procedure for asynchronous circuits as initiated by Huffman. For one thing, the three representations used in specifying an asynchronous circuit—the events graph, the word-recognition tree and the flow table (a slightly advanced version of Huffman's famous flow table)—are time-independent idealisations. This allows us to build on the theory of latches, as put forth in Part II, and to freely use logic in the same way as for combinational circuits and for latches. The basic problem confronting the standard synthesis procedure is finding a binary encoding for the flow table. Chapter 15 presents an algorithmic solution for the encoding problem. Another hitherto unsolved problem is that of verifying a sequential design. A solution to this problem is given in Chap. 18. Many of the methods and procedures of Part III are greatly improved and expanded versions found in Vingron (2004). I have refrained from a discussion of standard theory as there are excellent books on the subject (my favourites being Krieger (1969), and Dietmeyer (1971)).

Sections and chapters containing relevantly new material are marked by an asterisk (\*). Much of the information conveyed is contained in the figures which is why I have designed and drawn them very carefully. In general I would suggest

Preface ix

not to just fly over them. The index contains not only page numbers, rather it also refers to figures (as in: *see* Fig. 13.5) or equations (as in: *see* Eq. (13.5)). You will find the chapter number (e.g., Chap. 13) in the page headers. I always appreciate comments, and invite you to write me at *vingron@kabsi.at*.

Hinterbrühl Austria Shimon P. Vingron

#### **Contents**

#### **Part I Combinational Circuits**

| 1 | Logic | Variables and Events                | 3  |

|---|-------|-------------------------------------|----|

|   | 1.1   | Specifying a Circuit in Plain Prose | 3  |

|   | 1.2   | Analogue and Binary Timing Diagrams | 4  |

|   | 1.3   | Events Graph and Events Table*      | 7  |

|   | 1.4   | Logic Variables and Logic Formulas* | 9  |

|   | 1.5   | Drawing the Logic Circuit           | 11 |

| 2 | Switc | hing Devices                        | 13 |

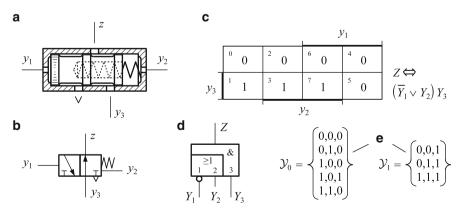

|   | 2.1   | Pneumatic Valves                    | 13 |

|   | 2.2   | Electric Relays                     | 17 |

|   | 2.3   | CMOS Transistors                    | 22 |

| 3 | Elem  | entary Logic Functions              | 27 |

|   | 3.1   | Logic Functions                     | 27 |

|   | 3.2   | Basic Gates                         | 30 |

|   | 3.3   | Using AND, OR and NOT               | 33 |

|   | 3.4   | Basic Laws                          | 34 |

|   | 3.5   | Single-Variable Formulas            | 35 |

|   | 3.6   | Commutative and Associative Laws*   | 36 |

|   | 3.7   | Distributive Laws*                  | 37 |

|   | 3.8   | Generalised DeMorgan Theorems       | 39 |

| 4 | Norm  | nal Forms                           | 41 |

|   | 4.1   | Minterms and Maxterms               | 41 |

|   | 4.2   | Canonical Normal Forms              | 43 |

|   | 4.3   | Using Canonical Normal Forms        | 44 |

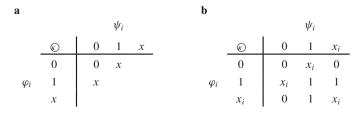

|   | 4.4   | Zhegalkin Normal Form               | 46 |

|   | 4.5   | Dual Zhegalkin Normal Form          | 48 |

xii Contents

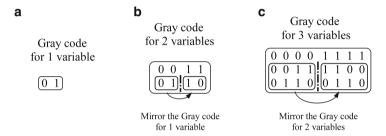

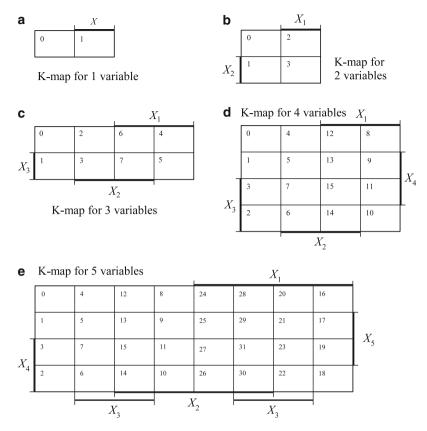

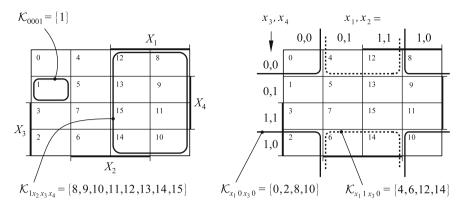

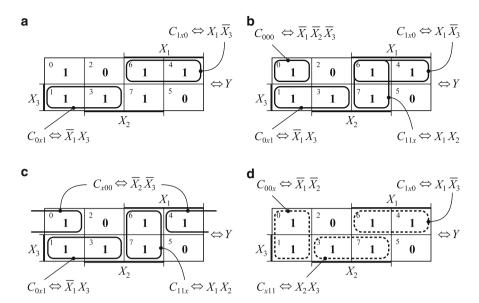

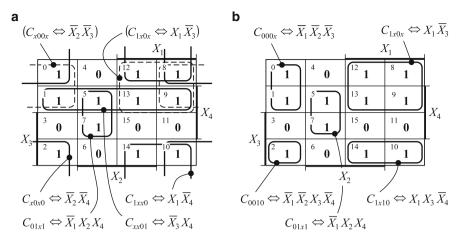

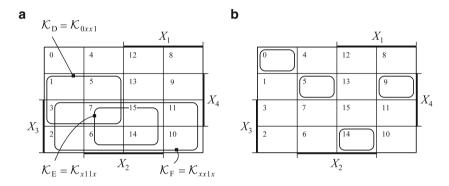

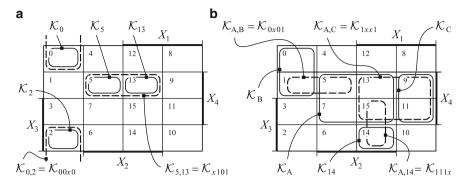

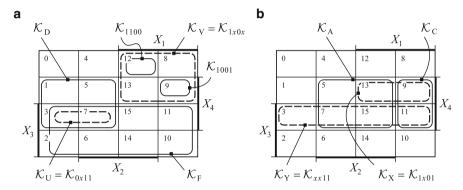

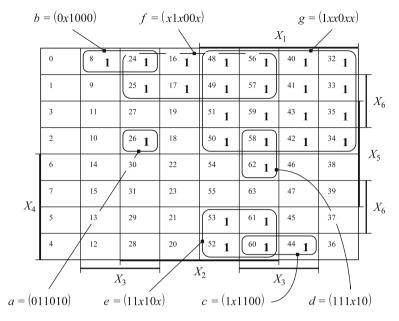

| 5   | Karn                   | augh Maps                                | 51  |

|-----|------------------------|------------------------------------------|-----|

|     | 5.1                    | How to Draw a Karnaugh Map               | 51  |

|     | 5.2                    | Karnaugh Set and Conjunctive Term        | 53  |

|     | 5.3                    | Proving and Developing Theorems          | 57  |

|     | 5.4                    | Evaluating Karnaugh Maps                 | 59  |

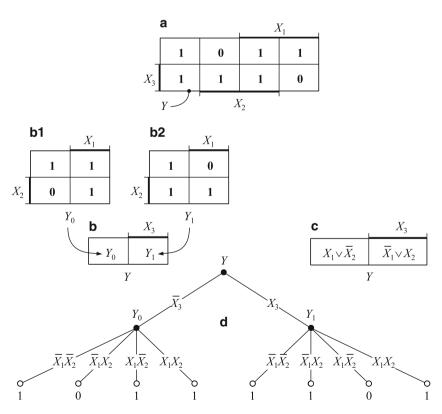

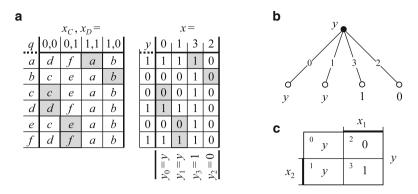

|     | 5.5                    | Karnaugh Trees and Map-Entered Variables | 63  |

| 6   | Adja                   | cency and Consensus                      | 67  |

|     | 6.1                    | Adjacent K-Sets and their Consensus*     | 67  |

|     | 6.2                    | Formalising Adjacency                    | 70  |

|     | 6.3                    | Formalising Consensus                    | 72  |

|     | 6.4                    | When Is One K-Set a Subset of Another?   | 73  |

| 7   | Algel                  | oraic Minimisation                       | 75  |

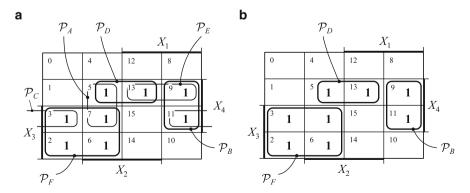

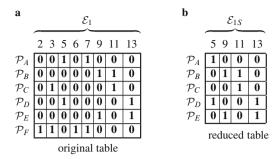

|     | 7.1                    | Finding the Full Cover*                  | 75  |

|     | 7.2                    | Finding Minimal Covers*                  | 78  |

|     | 7.3                    | Minimisation Considering Don't Cares*    | 81  |

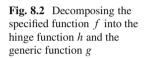

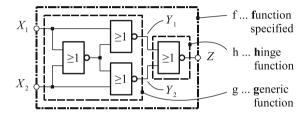

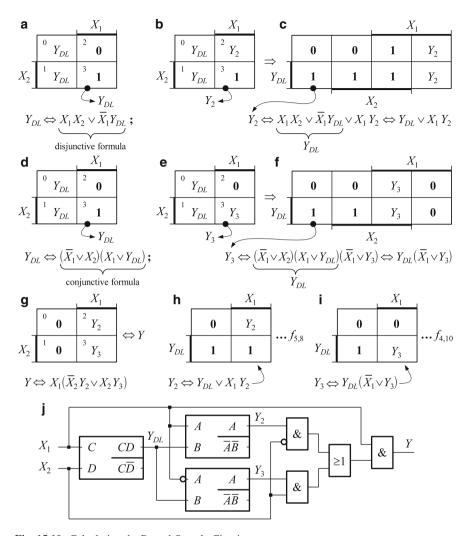

| 8   | Desig                  | n by Composition*                        | 85  |

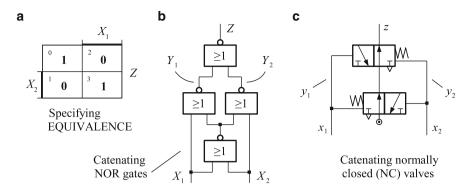

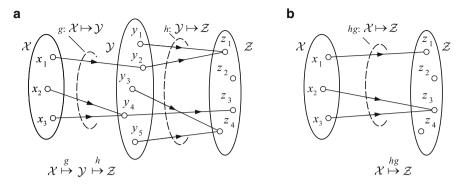

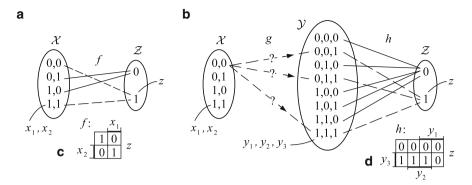

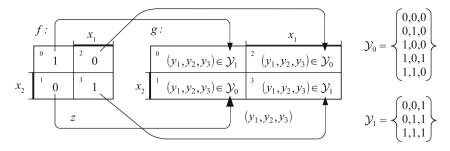

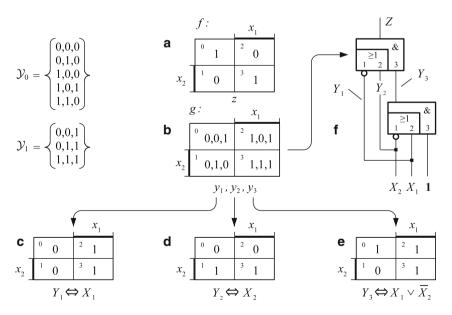

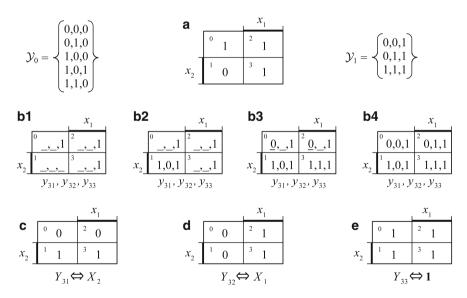

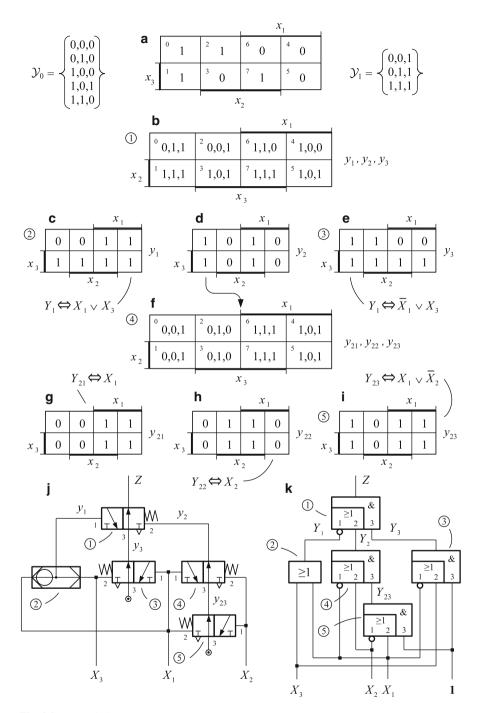

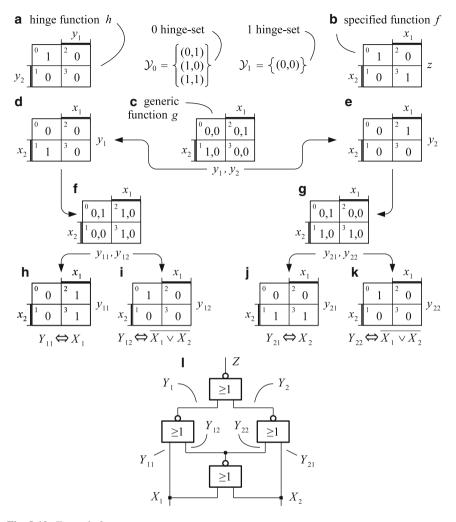

|     | 8.1                    | The Basic Concept                        | 85  |

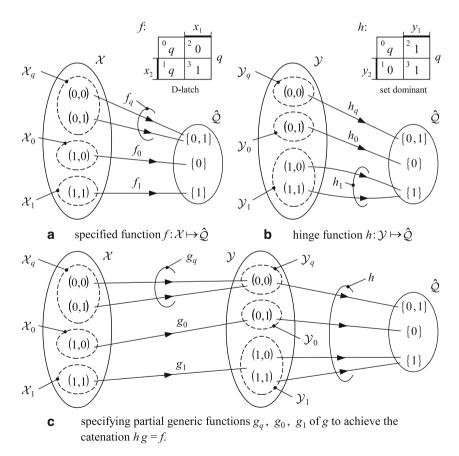

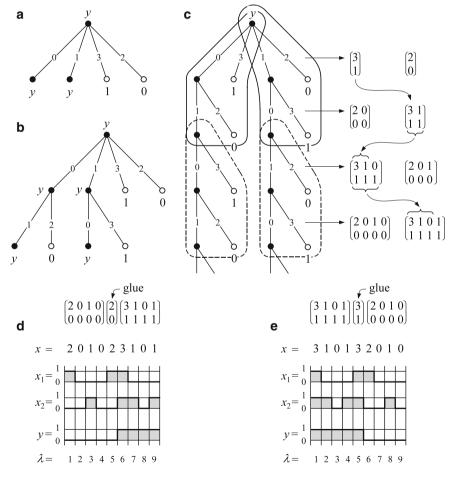

|     | 8.2                    | Catenation                               | 86  |

|     | 8.3                    | Visualising the Composition Problem      | 88  |

|     | 8.4                    | Choosing a Generic Function              | 89  |

|     | 8.5                    | Composing a Circuit: Example 1           | 91  |

|     | 8.6                    | Composing a Circuit: Example 2           | 95  |

|     | 8.7                    | Composing a Circuit: Example 3           | 95  |

| Par | t II I                 | Latches                                  |     |

| 9   | Rocio                  | Theory of Latches*                       | 99  |

| ,   | 9.1                    | What Is a Latch?                         | 99  |

|     | 9.2                    | The Memory Function                      | 101 |

|     | 9.2                    | Introducing Inclusions and Exclusions    | 101 |

|     | 9.3<br>9.4             | Basic Memory Evaluation-Formulas         | 104 |

|     | 9. <del>4</del><br>9.5 | Generalised Memory Evaluation-Formulas   | 108 |

|     |                        | •                                        |     |

| 10  | _                      | gning Feedback Latches*                  | 111 |

|     | 10.1                   | Feedback Evaluation-Formulas             | 111 |

|     | 10.2                   | Design and Memorisation Hazards          | 113 |

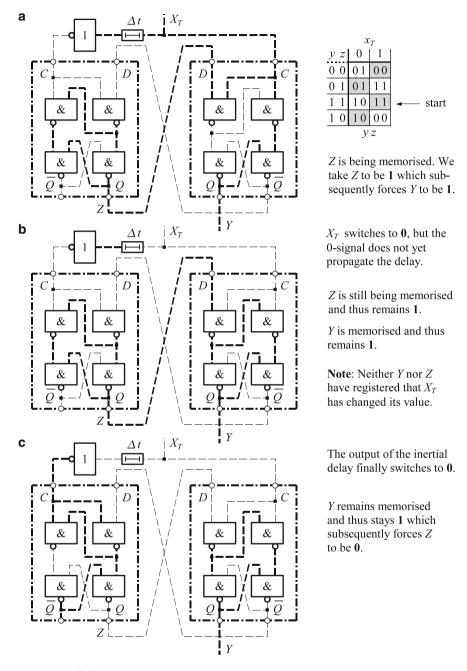

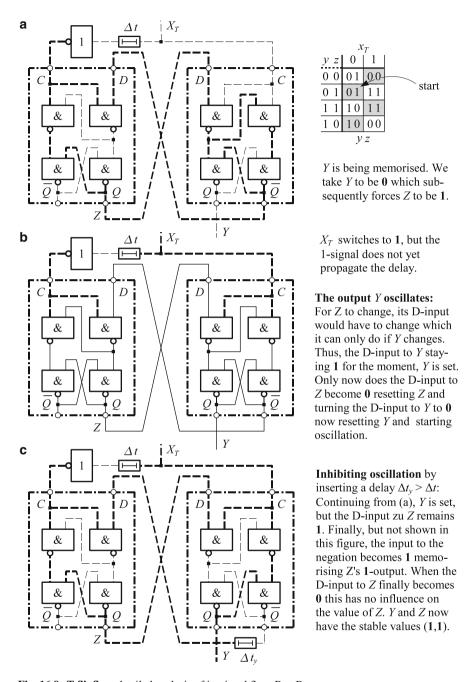

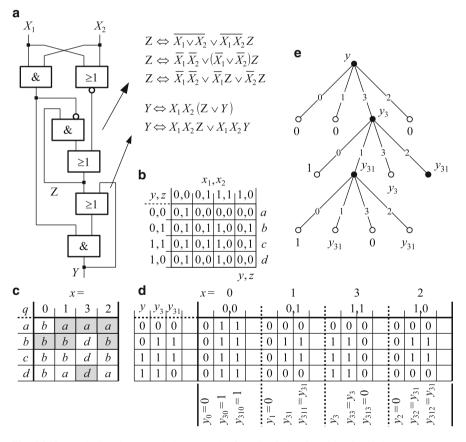

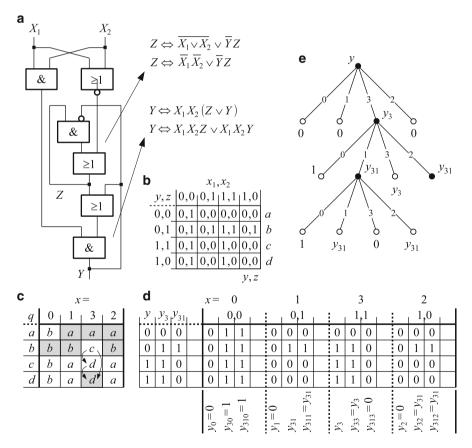

|     | 10.3                   | Delayed Feedback                         | 117 |

|     | 10.4                   | Pre-established Feedback                 | 120 |

|     | 10.5                   | Minimisation                             | 122 |

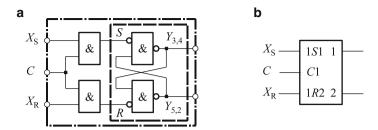

| 11  |                        | entary Latches                           | 125 |

|     | 11.1                   | Classification of Elementary Latches     | 125 |

|     | 11.2                   | Symbols for Elementary Latches*          | 128 |

|     | 11.3                   | Predominantly Memorising Latches*        | 130 |

Contents xiii

|     | 11.4  | Predominantly Setting and Resetting*      | 131 |

|-----|-------|-------------------------------------------|-----|

|     | 11.5  | Eccles-Jordan Latches—the Principle       | 134 |

|     | 11.6  | Eccles-Jordan Latches—Their Symbols*      | 136 |

|     | 11.7  | Standard Symbols for Latches              | 138 |

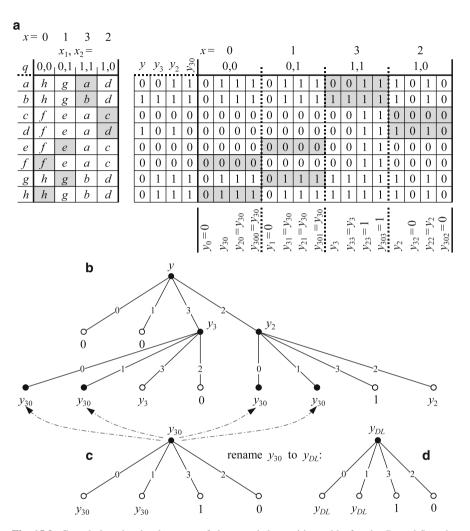

| 12  | Latcl | n Composition*                            | 141 |

|     | 12.1  | Principle of Latch Composition            | 142 |

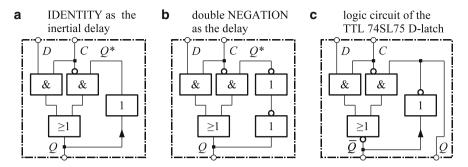

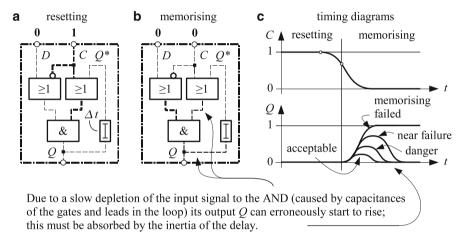

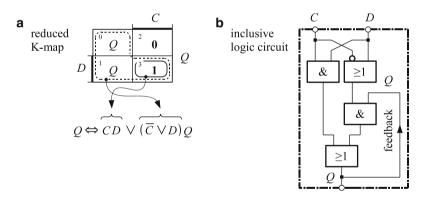

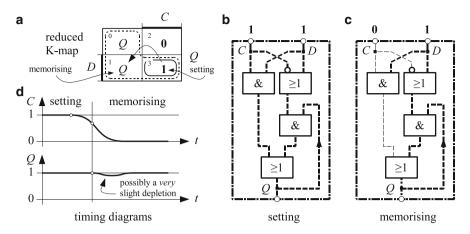

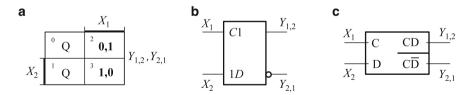

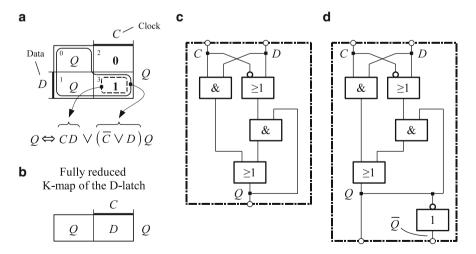

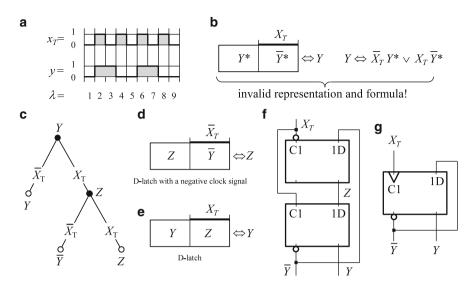

|     | 12.2  | D-Latch Designs                           | 146 |

|     | 12.3  | PSR-Latches Using NAND or NOR-Gates       | 150 |

|     | 12.4  | Synchronous Latch-Inputs                  | 153 |

| Par | t III | Asynchronous Circuits                     |     |

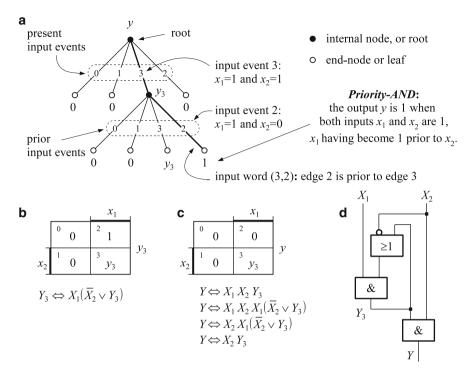

| 13  | Word  | I-Recognition Tree*                       | 157 |

|     | 13.1  | Priority-AND                              | 157 |

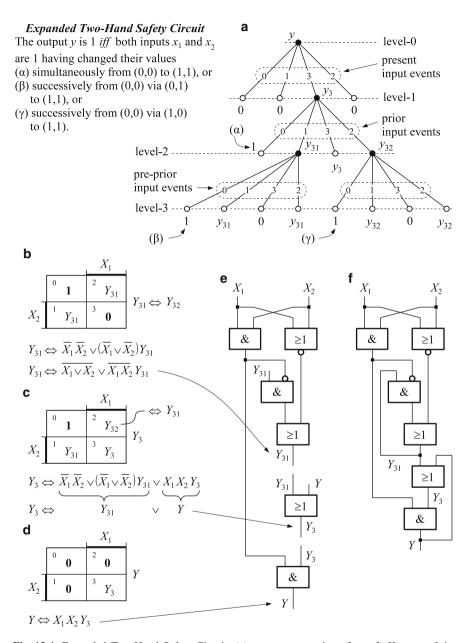

|     | 13.2  | Two-Hand Safety Circuit                   | 161 |

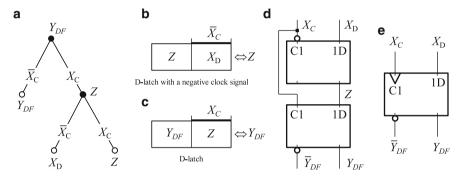

|     | 13.3  | D-Flipflop and T-Flipflop                 | 163 |

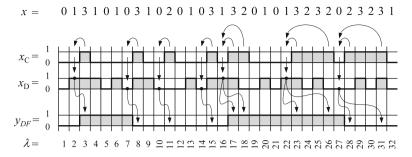

|     | 13.4  | JK-Flipflop                               | 166 |

| 14  | Huff  | man's Flow Table                          | 169 |

|     | 14.1  | Moore-Type Sequential Automaton           | 169 |

|     | 14.2  | Primitive Flow-Table                      | 172 |

|     | 14.3  | Specifying Priority-AND Circuits          | 173 |

|     | 14.4  | Sampling and Synchronising                | 175 |

|     | 14.5  | Passed-Sample Problem                     | 178 |

|     | 14.6  | Expanded Two-Hand Safety Problem          | 182 |

|     | 14.7  | From Flow Table to Events Graph           | 184 |

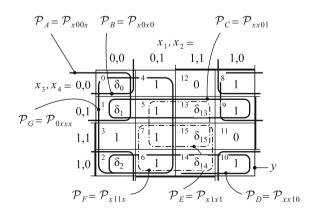

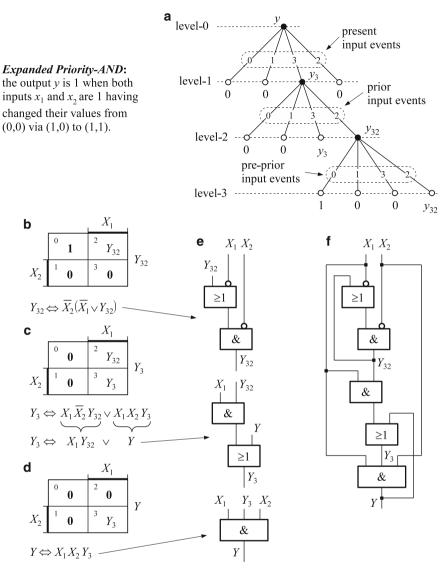

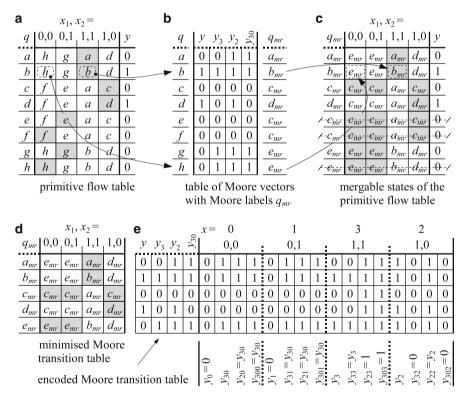

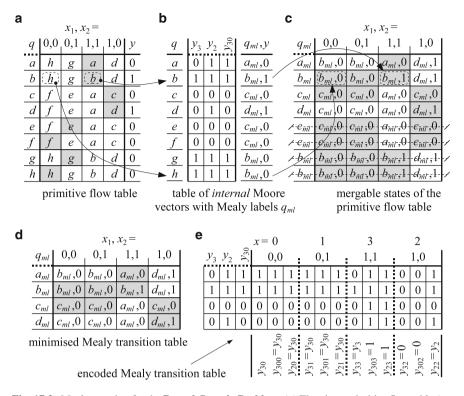

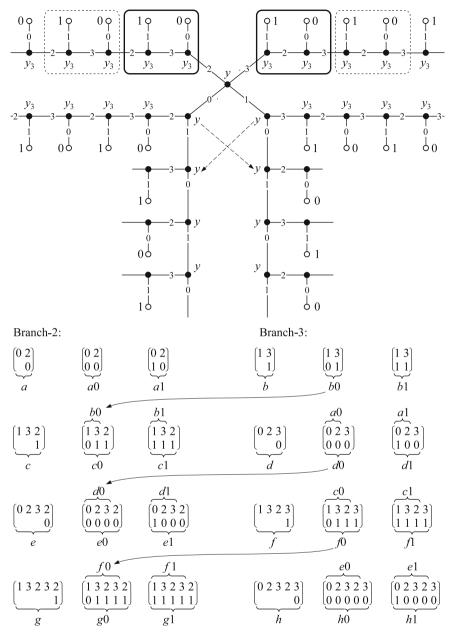

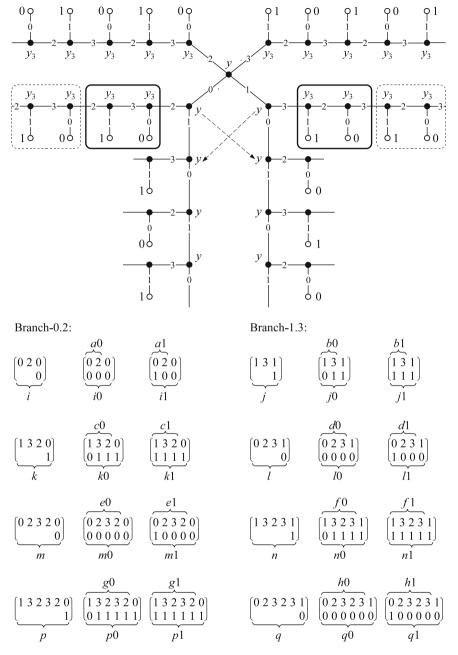

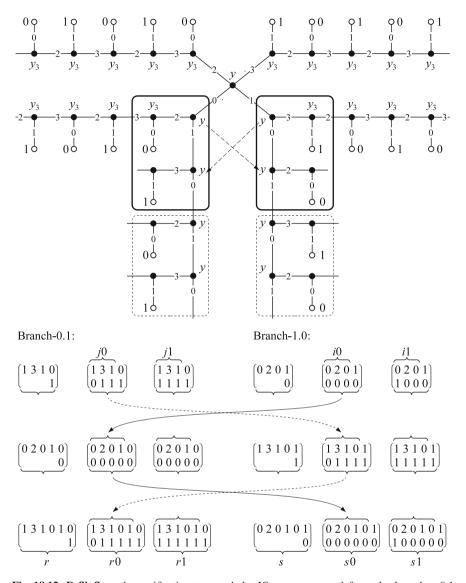

| 15  | State | -Encoding by Iterative Catenation*        | 187 |

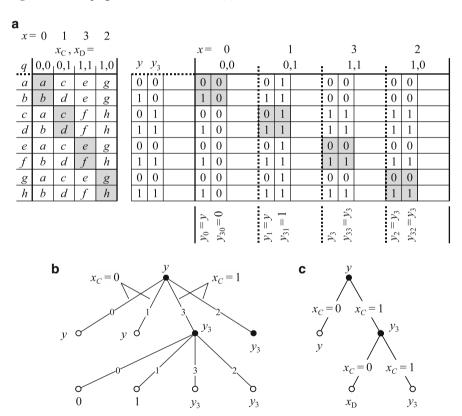

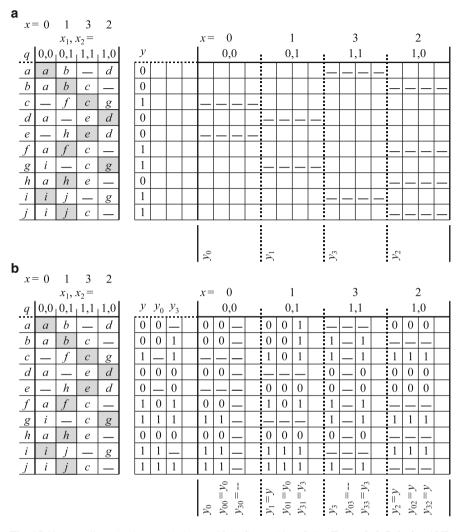

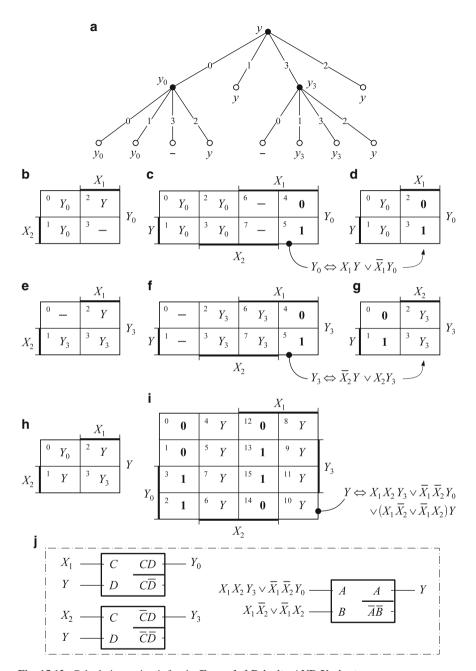

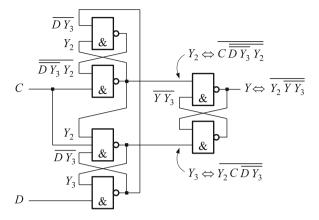

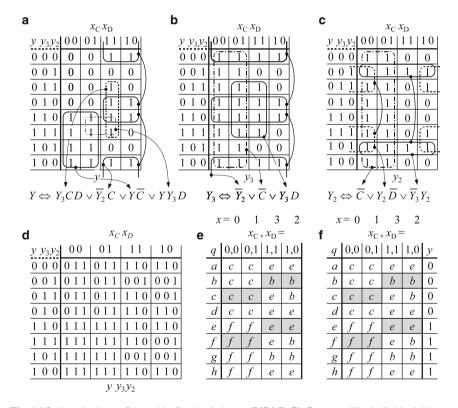

|     | 15.1  | Catenation: From Moore to Mealy           | 187 |

|     | 15.2  | Iterative Catenation                      | 189 |

|     | 15.3  | Expanded Priority-AND                     | 190 |

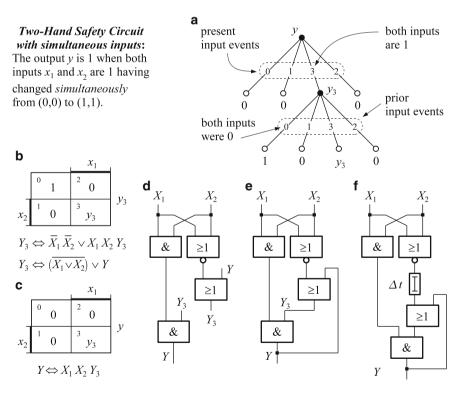

|     | 15.4  | Two-Hand Safety Circuits                  | 192 |

|     | 15.5  | D-Latch and D-Flipflop                    | 193 |

|     | 15.6  | Passed-Sample Circuit                     | 195 |

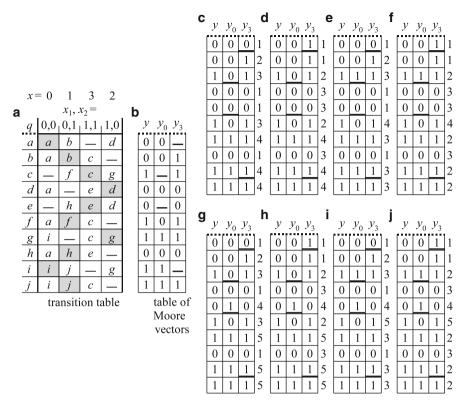

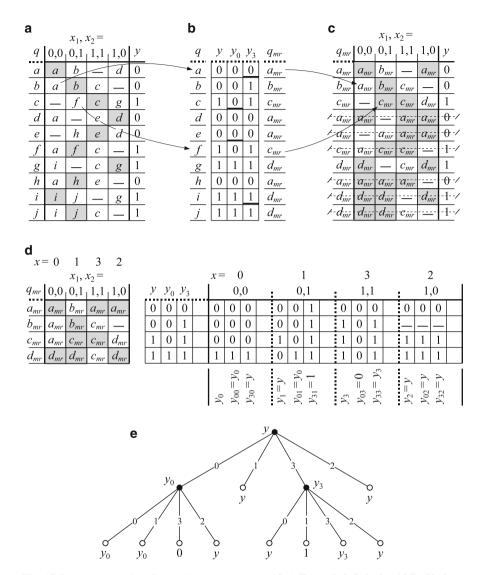

|     | 15.7  | Incompletely Specified Flow Tables        | 199 |

| 16  |       | uit Analysis                              | 203 |

|     | 16.1  | Analysing a Circuit's External Behaviour  | 203 |

|     | 16.2  | Formalistic Analysis of State Transitions | 206 |

|     | 16.3  | Realistic Analysis and Essential Hazards  | 208 |

|     | 16.4  | Avoiding Essential Hazards                | 214 |

| 17  |       | Reduction*                                | 217 |

|     | 17.1  | Merging Toward a Moore Flow Table         | 218 |

|     | 17.2  | Merging Toward a Mealy Flow Table         | 220 |

xiv Contents

|      | 17.3       | Merging Incompletely Specified Tables    | 222 |

|------|------------|------------------------------------------|-----|

|      | 17.4       | Mealy-Type Sequential Automaton          | 224 |

| 18   | Verif      | ying a Logic Design*                     | 227 |

|      | 18.1       | End-Nodes and Their Event Graphs         | 227 |

|      | 18.2       | Verification Tree and Verification Graph | 229 |

|      | 18.3       | Verification Table                       | 234 |

|      | 18.4       | Verification Graph for the JK-Flipflop   | 237 |

|      | 18.5       | Verification Graph for the D-Latch       | 238 |

|      | 18.6       | Verification Graph for the D-Flipflop    | 239 |

| Glos | ssary .    |                                          | 245 |

| Bibl | liogra     | phy                                      | 251 |

| Inda | o <b>v</b> |                                          | 253 |

## **Chapter 1 Logic Variables and Events**

Switching circuits process binary input signals logically, the result itself being a binary output signal. The logical operations used in processing the input signals require the binary signals to be transformed into logic variables. Giving substance to the previous two sentences is the subject of this chapter.

The first three sections concentrate on the *specification* of circuits, here, Sect. 1.3 introducing two tools of importance: the *events graph* and the *events table*. The prime result of this chapter is the introduction of *logic variables* and *logic formulas* in Sect. 1.4.

#### 1.1 Specifying a Circuit in Plain Prose

Let us employ a running example of a switching circuit to introduce some basic concepts. As formal methods for describing a circuit's behaviour are, as yet, lacking, we shall do the obvious, and use plain prose to specify a **running example**:

Imagine a windowless room with two doors and a light switch at each door. Every time someone passes through a door (to become the sole occupant of the room, or to leave it empty) he brings the switch next to that door from its current to its alternative position, thereby switching the lights on if they were off, and off if they were on. Correspondingly, the room's lights go on if they were off, and vice versa, go off if they were on. Thus, the basic idea is: whenever someone enters the room he turns the electric lights on, and then turns them off when he leaves the room by the same, or by the other door.

Our task is to design a circuit that takes as its two input signals the current (or voltage) from the two switches, and produces as output signal the lighting condition in the room.

There are a few things to note in the above specification. Firstly, care was taken to state the number of inputs and outputs to the circuit. Secondly, each of

the circuit's signals occurs in either of two distinctly different states: The current, voltage, or lights are either on or off. Signals with this property are called **binary signals**. Usually the two alternative states of a binary signal are referred to by the integers 0 and 1. The 0 is most frequently associated with the lower energy level of a binary signal, the 1 with the higher energy level (If the energy level of a signal's state is irrelevant, one is free to associate 0 and 1 with the signal's states in any way convenient). Less obvious aspects of the above specification are: The wording of the specification is **redundant**. For human beings redundancy is helpful in grasping things more quickly, and often more thoroughly. Formal systems (on the other hand) need no redundancy (whatsoever). Finally, the above *specification is complete*, meaning that it contains all the information needed to design the circuit; you will soon see how this statement can be verified.

#### 1.2 Analogue and Binary Timing Diagrams

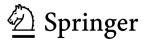

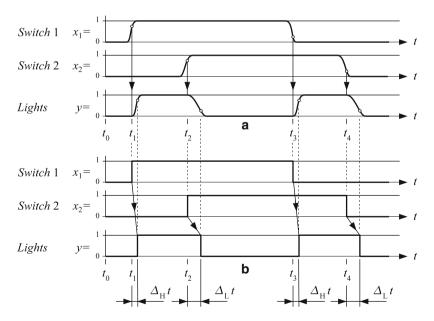

Casting the usually cumbersome verbal specification into a technical form is frequently done via a **timing diagram**, a diagram which depicts the time-dependent behaviour of a signal. A timing diagram for our running example is shown in Fig. 1.1. This being our first acquaintance with a timing diagram, we ponder it and its relationship to the *running example* quite conscientiously.

- $t_0$ : At an arbitrarily chosen starting time,  $t_0$ , when you open a door to enter the room, assume that the contacts of both switches are open letting no current flow. Accordingly, we interpret both input signals to the circuit to be 0. The lights will be off, and we again choose the integer 0 to describe this state.

- $t_1$ : Entering the room, you activate, say, switch 1. The current that can now flow over the closed contacts of the switch is referred to (when flowing freely) by the integer 1. But, current cannot *jump* from a zero value to its maximum value: It first rises slowly, then ever faster until it almost reaches its maximum value from when on it grows ever more slowly towards its maximum of 1. Only at time  $t_1$ , when the current has reached a certain height (say, 80% of the

Fig. 1.1 A timing diagram of the running example

maximum value), will the circuit register that the input signal has become 1, and will *start* turning the lights on. As with the current, it takes time for the lights to obtain their full brightness, as the form of the post- $t_1$  output signal depicts.

- $t_2$ : You walk through the room leaving it via the opposite door and bringing switch 2 into its alternative state (a value of 1 for switch 2) to turn the lights off as you leave (letting the value for the lights drop to zero). Again, note the gradual rise of the value for  $x_2$ , and the gradual decline of the output value y.

- $t_3$ : To turn the lights on, a person entering the room tips the switch at hand (say switch 1). Please take a few moments to consider the relationship between the declining signal  $(x_1)$  and the rising signal (y).

- *t*<sub>4</sub>: When leaving the room by the opposite door, switch 2 will be brought to its alternative state to turn the lights off.

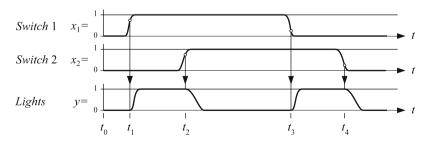

We now take a closer look at the concept of a signal, and the way analogue signals are transformed into binary signals. A **signal** is the information carried by, or contained in, a quantifiable physical entity (such as voltage, speed, force, etc.). Colloquially, the physical entity itself (and not the information it carries) is frequently called the signal. To be independent of any physical entity and its units of measurement (e.g., Volt, m/s, Newton) we let any physical entity being considered vary *continuously* between 0 and 1. Signals that can change their values continuously are called **analogue signals**. An example of an analogue signal is given in Fig. 1.2a. For all practical purposes, physical entities in a real-world environment

Once the input signal exceeds the high value *H*, the output jumps to 1 and remains 1 until the input signal drops below the low value *L*.

Once the input signal drops below the low value L, the output jumps to 0 and remains 0 until the input rises above the high level H.

Fig. 1.2 Transforming an analogue signal (a) into a binary signal (b) with the help of an ideal hysteresis (c)

change their values continuously. But switching circuits use **binary signals**, signals whose values are either 0 or 1, and thus are supposed to *jump instantaneously* from one value to another. Clearly, it is quite a challenge to transform real-world analogue signals into binary signals. This is done with the help of an ideal **hysteresis**, a function with an input for the analogue signal, and an output for the binary signal. The input-output behaviour of the hysteresis is shown in Fig. 1.2c and explained in the text of the figure. Electronically, the ideal hysteresis is well approximated by a circuit known as a Schmitt trigger.

Let us apply the hysteresis function to the analogue signal of Fig. 1.2a. The instant the analogue signal (which is fed into the hysteresis) is switched on, it starts rising, first slowly and then with ever increasing speed. Only when it reaches a certain high level H does the output of the hysteresis jump from 0 to 1. Note the time lag  $\Delta_H t$  from the instant the analogue signal is switched on to the moment when the binary output signal becomes 1. The analogue signal continues to rise until it reaches its 1-value. When it is switched off, it starts declining. Only when it has dropped to low level L does the output signal of the hysteresis jump from 1 to 0. Here too, we register a time delay,  $\Delta_L t$ , from when the analogue signal is switched off to the moment the binary signal drops to 0.

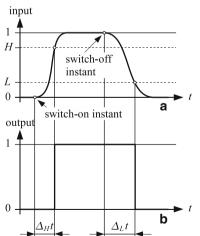

We are now well equipped to transform our *analogue* timing diagram, repeated in Fig. 1.3a, into its *binary* equivalent of Fig. 1.3b. As the instant when an *input* signal jumps from 0 to 1, we choose the moment when the analogue signal reaches the H-level. As the instant when an *input* signal jumps from 1 to 0, we choose the moment when the analogue signal drops to the L-level. The instantaneous

Fig. 1.3 Developing the binary timing diagram (b) from an analogue timing diagram (a)

zero-to-one transitions, and the one-to-zero transitions of the *output* signal are governed by the concept of an ideal hysteresis.

The **binary timing diagram** of Fig. 1.3b implies a causal dependence of the output signal y on the input signals  $x_1$  and  $x_2$  that is quite misleading. The implication is that the **rising edge** of  $x_1$  at  $t_1$  causes the output y to jump (instantaneously) from 0 to 1 after the time interval  $\Delta_H t$  has elapsed. On the other hand, the rising edge of y at  $t_3 + \Delta_H t$  seems to be caused by the **falling edge** of  $x_1$  at  $t_3$ . Do note that, in a like manner, both the rising and falling edges of  $x_2$  seem to cause the falling edges of y. If we wanted to design circuits along these lines, we would quickly find ourselves in rather deep water. To avoid this, we introduce an idealisation that allows a simpler conceptual and mathematical approach.

#### 1.3 Events Graph and Events Table\*

Mathematically, the problem with the binary timing-diagram of Fig. 1.3b is that the output variable y is *not* a function of the ordered pair  $(x_1, x_2)$  of input variables  $x_1$  and  $x_2$ : Every occurring input pair—(0,0),(0,1),(1,0), and (1,1)—maps to 0 as well as to 1. Let it suffice to point this out for only one input pair, for  $(x_1, x_2) = (1,1)$  which is present from  $t_2$  to  $t_3$ . From  $t_2$  to  $t_2 + \Delta_L t$  the output is 1, while from  $t_2 + \Delta_L t$  to  $t_3$  the output is 0. As can be seen from the diagram of Fig. 1.3b, the problem with two output values per input pair stems from the presence of the time lags  $\Delta_L t$  and  $\Delta_H t$ .

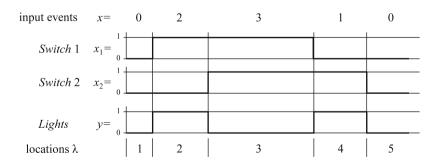

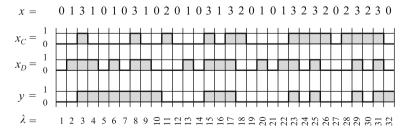

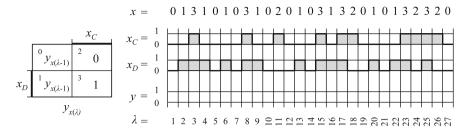

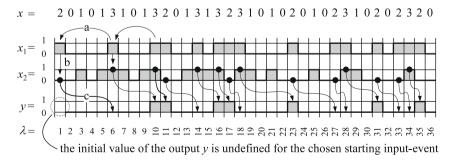

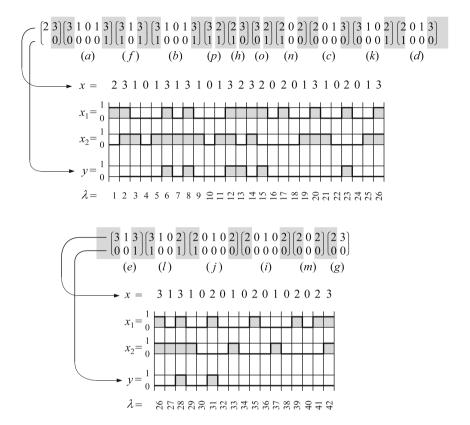

To remedy this situation we postulate circuits to be **well-behaved**, that is, the output may only change when the value of at least one input variable changes, which does not mean that the output must change when an input variable changes its value. In general not every change of an input value necessitates a change in the output value. As desired, postulating that a circuit be well behaved reduces the time delays in Fig. 1.3 to zero. We call the *binary timing-diagram of a well behaved circuit* an **events graph**. The events graph for our running example is shown in Fig. 1.4.

Fig. 1.4 An events graph for the running example

Superficially, the events graph seems to differ insignificantly from the binary timing diagram. But the basic and very important difference is that the events graph is *not* a time dependent representation of signals.

The events graph consists of a sequence of *input events* and associated output values, an **input event** being an ordered n-tuple  $(e_1, e_2, \ldots, e_n)$  of arbitrary but fixed values  $e_1, e_2, \ldots, e_n$  of the input variables  $x_1, x_2, \ldots, x_n$ , respectively. One draws the input events of an events graph successively from left to right in a sequence one finds appropriate in describing the problem at hand, parting two neighbouring input events by vertical lines, and then numbering the sequence of input events successively from left to right; each of these numbers is called a **location**  $\lambda$ , and gives the position of an input event x (together with the associated output value) within the chosen sequence of input events.

The output value in a location is constant because we postulate our circuits to be well behaved. As no signal, neither input nor output signal, changes its value between the vertical lines it is irrelevant how far apart they are drawn. Frequently, one draws them in equal distances.

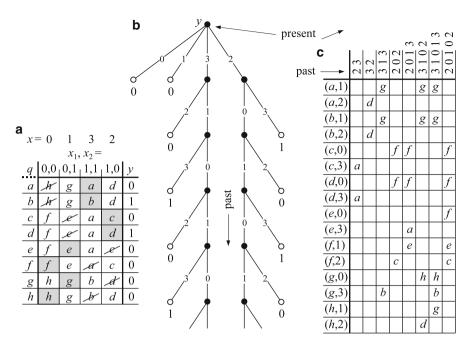

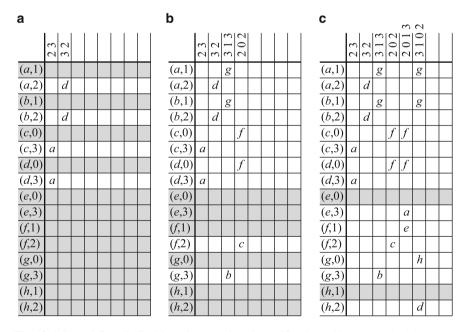

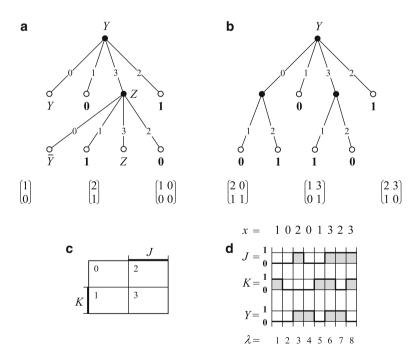

The events graph for our running example has the important property of expressing the output value of the circuit as a *function* of the input values. A **function** always maps the input event, an ordered n-tuple  $(e_1, e_2, \ldots, e_n)$  of individual input values  $e_1, e_2, \ldots, e_n$ , to one and the same output value, and does so for each input event. For instance, at locations 1 and 5 the input event is (0,0) which in both cases is mapped to the output value 0. If, at location  $\lambda = 5$ , the output were 1, the output would not be a *function* of the input events—it would be a *relation*. A **relation** will map at least one input event to more than one output value. An events graph which depicts the output values as a *function* of the input events specifies a **combinational circuit**; in the case of a *relation* it specifies a **sequential circuit**. Sequential circuits are the topic of Parts II and III.

Each individual value  $e_i$  of an input event  $(e_1, e_2, \dots, e_n)$  is, in the case of binary circuits, either 0 or 1 so that each such event represents an n-digit binary number. Most frequently we express these binary numbers by their decimal equivalents

$$e = \sum_{i=1}^{n} e_i \cdot 2^{n-i}.$$

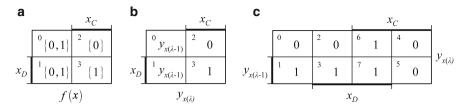

It is characteristic for an events graph of a *combinational* circuit that whenever a certain input event *e* is depicted, it initiates the same output value. This possible redundancy in the representation is avoided when using an *events table* instead of an events graph. The **events table** has one column for each input event, the bottom row containing the output values (unique for each input event). The events table for our running example is shown in Fig. 1.5a.

<sup>&</sup>lt;sup>1</sup>In other words: We draw a vertical line whenever at least one input variable changes its value.

| $\mathbf{a}$ $\lambda_5$ |             |             |             | b |            |   |          |   |   |

|--------------------------|-------------|-------------|-------------|---|------------|---|----------|---|---|

| $\lambda_1$              | $\lambda_4$ | $\lambda_2$ | $\lambda_3$ |   | x =        | 0 | 1        | 2 | 3 |

| $x_1 = 0$                | $x_1=0$     | $x_1=1$     | $x_1=1$     |   | $x_1 =$    | 0 | 0        | 1 | 1 |

| $x_2 = 0$                | $x_2 = 1$   | $x_2 = 0$   | $x_2 = 1$   |   | $x_2 =$    | 0 | 1        | 0 | 1 |

| y=0                      | y=1         | y=1         | y=0         |   | <i>y</i> = | 0 | 1        | 1 | 0 |

|                          | Expli       | cit form    | 1           |   |            | В | rief for | m |   |

Fig. 1.5 Events table corresponding to the events graph of Fig. 1.4

For clarity (i.e., to concentrate better on the information—the 0s and 1s—of the table), as well as to reduce the amount of writing necessary, we usually use the events table in its **brief form**, shown in Fig. 1.5b, in which the variables have been 'extracted' from the columns of each row. From the top to the penultimate row, the succession of 0s and 1s of a single column is its input event e. An events table whose variables are not extracted is called the **explicit form** of the table.

An advantage of the events table is that it enables us to recognise when a combinational circuit is **completely specified**; this is the case when an *output value*, either a 1 or a 0, is specified for every input event, i.e., for every column. If a circuit specification does not state what output value is initiated by each of the input events, it is said to be **incomplete**. Most technical problems—thankfully—lead to incompletely specified circuits allowing us to choose output values which lead to simpler realisations. Our running example, as mentioned, is completely specified.

In the next section we turn to the interpretation of the events table, this leading us directly into the field of logic.

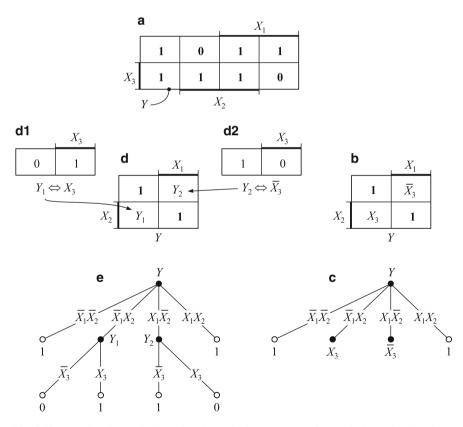

#### 1.4 Logic Variables and Logic Formulas\*

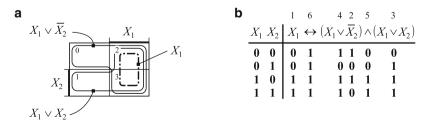

The events table is a tool of major importance: Not only does it enable an *unambiguous specification* of a combinational circuit, its analysis also leads directly to the introduction of *logic variables* and to the *logical evaluation of functions*. Let us start with an informal, yet stringent, interpretation of the events table of our running example, the table repeated below. It states when the output *y* is 0 and when it is 1. This is expressed in a semi-formal manner in the sentence next to the table.

$$\begin{vmatrix} x_1 = 0 & x_1 = 0 & x_1 = 1 & x_1 = 1 \\ x_2 = 0 & x_2 = 1 & x_2 = 0 & x_2 = 1 \\ y = 0 & y = 1 & y = 1 & y = 0 \end{vmatrix}$$

The output variable y is 1 if and only if  $x_1$  is 0 AND  $x_2$  is 1 OR  $x_1$  is 1 AND  $x_2$  is 0

Employing the symbols

$\Leftrightarrow$  ... for logically equivalent or if and only if (iff),

$\wedge$  ... for AND, and

∨ ... for OR

the sentence to the right of the table can be written as:

$$(y = 1) \Leftrightarrow ((x_1 = 0) \land (x_2 = 1)) \lor ((x_1 = 1) \land (x_2 = 0)).$$

(1.1)

Before continuing, take a few moments to ponder the above formula, more precisely, the expressions y=1,  $x_i=0$ , and  $x_i=1$  in the inner parentheses. Stating that a certain input variable  $x_i$  is 0 does *not* mean that  $x_i$  really is 0. In fact, we have to *measure* the value of  $x_i$  to know its value. Let us refer to a measured value of  $x_i$  as an **instance** of  $x_i$ . We could then substitute the measured value, its instance, for  $x_i$  in  $x_i=0$  obtaining either 0=0 or 1=0, as the case may be. These expressions are *propositions*. A **proposition** is a statement that is either **true** (which we denote as **1**) or **false** (denoted as **0**). The term  $x_i=0$ , on the other hand, has only the *form* of a proposition, and is thus called a **propositional form**; it acts as a *logic variable*, a variable whose value is either **1** or **0**. Specifying each input  $x_i$  to have a certain value, and stating the associated value of the output y, provides us with a single column of the events table.

The rather cumbersome expression (1.1) is greatly simplified by introducing the following **logic variables**  $X_i$ ,  $\overline{X}_i$ , Y, and  $\overline{Y}$  as a shorthand notation for the expressions written within the inner parentheses, i.e. defining

Rewriting (1.1) with the help of the logic variables  $X_i$ ,  $\overline{X}_i$ , Y, and  $\overline{Y}$  leads to what is called a **logic formula** or **Boolean formula**<sup>2</sup>:

$$Y \Leftrightarrow (\overline{X}_1 \wedge X_2) \vee (X_1 \wedge \overline{X}_2). \tag{1.3}$$

Colloquially, the symbol  $\Leftrightarrow$ , called **logical equivalence**, refers to its left and right sides being equal from the point of view of logic, allowing us—among other things—to use the left-hand and right-hand expressions interchangeably in logic formulas (substituting one by the other). For a detailed discussion of logic equivalence see Chap. 8. The symbol : $\Leftrightarrow$  takes a (single) logic variable on its left, this being used as a shorthand notation for a logic expression on the right of the symbol : $\Leftrightarrow$ . The symbol : $\Leftrightarrow$  can be read as '... is defined to be logically equivalent to ...'.

<sup>&</sup>lt;sup>2</sup>For a stringent explanation of what a logic formula is, please refer to Sect. 8.1.

Alternatively to stating when y is 1, we could have used the events table to state precisely when the output variable y is 0, writing this in analogy to (1.1) as

$$(y = 0) \Leftrightarrow ((x_1 = 0) \land (x_2 = 0)) \lor ((x_1 = 1) \land (x_2 = 1)),$$

(1.4)

which, with (1.2), may be written as the logic formula

$$\overline{Y} \Leftrightarrow (\overline{X}_1 \wedge \overline{X}_2) \vee (X_1 \wedge X_2).$$

(1.5)

The formulas (1.3) and (1.5) are said to be **complementary**.

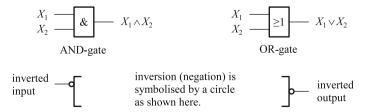

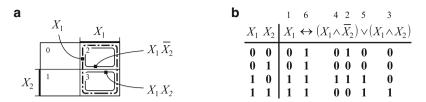

#### 1.5 Drawing the Logic Circuit

A logic circuit is comprised of **gate**, these being graphic symbols representing logic connectives. The gates for AND, OR and NOT (INVERSION) are shown in Fig. 1.6. To invert an input signal you draw a small circle where the input signal enters the gate. If you want to invert an output signal, you draw a small circle where the output signal leaves the gate.

Logic formulas, as (1.3) and (1.5), state which gates to use and how to connect them.

**Connecting gates to create a logic circuit.** To transform a logic formula into a circuit consisting of gates, you draw an AND gate for each  $\land$ -connective of the formula, and an OR-gate for each  $\lor$ -connective. The arguments of the  $\land$ - and  $\lor$ -connectives in the logic formula are taken as inputs to the associated gates, this ensuring the correct connection between the gates.

Some people like to draw a circuit starting with the innermost parentheses of a formula, thus drawing the circuit from the inputs to the output. Others prefer to start with the outermost parentheses, thus drawing the circuit from the output to the inputs. Use whichever method you feel more comfortable with.

The logic circuits of Fig. 1.7 all represent the same formula, i.e. (1.3). Figure 1.7b demonstrates that you can stretch a gate to a desired size, while Fig. 1.7c shows that

Fig. 1.6 Gates as graphical symbols for logical connectives

**Fig. 1.7** Drawing the circuit for  $Y \Leftrightarrow (\overline{X}_1 \wedge X_2) \vee (X_1 \wedge \overline{X}_2)$

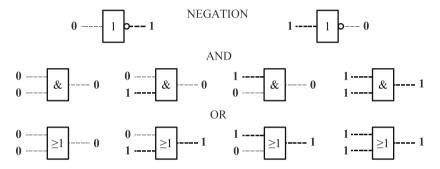

Fig. 1.8 Explaining the behaviour of NEGATION, AND, and OR

gates may be densely packed. The output signal, by the way, need not be positioned in the middle of a gate.

To fully understand these gates, we need to know precisely how their output signals react to the input signals. This is shown in Fig. 1.8 for the NEGATION, AND gate, and OR gate. Thick input or output lines represent TRUTH (i.e. 1), thin lines indicate FALSITY (i.e. 0).

## **Chapter 2 Switching Devices**

Logic gates, as introduced in the previous chapter, represent the connectives used in logic formulas. Assume you have drawn a circuit diagram using logic gates, and you now want to build the circuit using switching devices of a given technology (pneumatic, electric, or electronic). To be able to do so you need to know how to translate each logic symbol into a symbol or a collection of symbols of the technology you intend to employ. This chapter is restricted to discussing symbols used for pneumatic valves, electric relays, and CMOS transistors, and to showing how they correspond to logic gates.

In general, any quantifiable physical entity (such as voltage, pressure, force, etc.) can be used as a signal. To be independent of the actual physical entity of any binary signal (and its unit of measurement, such as Volt, psi, Newton, etc.) it is convenient and customary to map its two values to the *integers* 0 and 1. If nothing is said to the contrary, the smaller numerical value of a signal is mapped to 0, while the larger numerical value is mapped to 1, and these two integers are not assigned any unit of measurement. In this book the lower case letters x and y (most often with indices) shall always be used as variables whose range is  $\{0,1\}$  (denoted as  $x,y\in\{0,1\}$ , and meaning that the value of x and that of y is—in any given moment—either 0 or 1), and referred to as a binary **numeric variables**. These variables, x and y, are used to denote the input and output signals of actual switching devices and their symbols.

#### 2.1 Pneumatic Valves

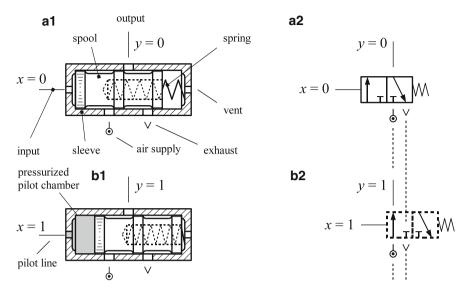

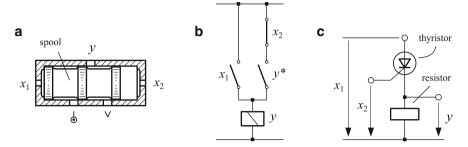

One of the most common pneumatic valves is the *spool-and-sleeve* design, the principle of which is shown in Fig. 2.1. A *zero* signal refers to atmospheric pressure, a *one* signal to a pressure of say 90 psi (pounds per square inch). If the pilot pressure is 0 the valve is said to be non-actuated and a spring presses the spool in the leftmost position. Actuating the valve by applying a 1-signal to the pilot chamber causes the

14 2 Switching Devices

Fig. 2.1 A normally open valve

spool to be pressed to the right (against the force of the spring). In the non-actuated valve you will notice that the output port and the exhaust port are connected while the air supply is blocked. In the actuated valve the output is connected to the air supply and the exhaust is blocked. Let us refer to this valve as a **normally open valve** (or **NO-valve**, for short), this naming convention being borrowed from the realm of electric relays. *Normal* refers to the pilot pressure x being 0 (the valve is not actuated), whereas *open* refers to the path between the air supply and the output being *interrupted*. The standard symbol for the NO-valve is that of Fig. 2.1a2. The rectangle to which the spring is attached (in our case, the right rectangle) shows the port connections in the non-actuated (the *normal*) case, the left rectangle depicts the port connections in the actuated case.

I took the liberty of drawing the *controlled lines*—exhaust, air supply, and output—as being detached from the symbol's rectangles to better show how the symbol is to be understood in the actuated case: Think of the controlled lines as being static and the rectangles being pushed to the right by the pilot pressure, as indicated in Fig. 2.1b2. When the valve is not actuated, the spring pushes the rectangles back into the position shown in Fig. 2.1a2. In actual use, the controlled lines are always drawn attached to the rectangle (the one with the spring), and *the symbol is always drawn in the* non-actuated *mode*. It is *never* drawn in the actuated mode indicated in Fig. 2.1b2. By **convention**, all device symbols in a circuit are drawn in their **normal state**—i.e., their non-actuated mode—which means that they are drawn as if their input signals were zero.

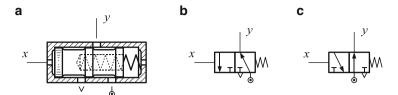

An alternate behaviour to the NO-valve is obtained if the air supply and the exhaust are interchanged as shown in Fig. 2.2a. When the valve is *not* actuated the

2.1 Pneumatic Valves 15

Fig. 2.2 A normally closed valve

output is connected to the air supply while actuating the valve connects the output to the exhaust. This behaviour is described by either of the symbols of Fig. 2.2b, c, and the valve is called a **normally closed valve** or **NC-valve**.

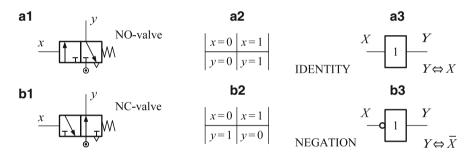

To analyse the behaviour of a spool-and-sleeve valve (Fig. 2.3) it suffices to work with the valve symbol. The input-output behaviour of such a valve is best documented in events tables as shown in Fig. 2.3a2, b2.

Fig. 2.3 Spool-and-sleeve valves as power amplifiers

According to the ATE of Fig. 2.3a2, 'the output y is 1 iff the input x is 1', or (in falling back on Sect. 1.4)

$$y = 1 \Leftrightarrow x = 1,$$

$$Y \Leftrightarrow X,$$

this function being called the IDENTITY, as the output Y is always identical to the input X. The symbol for the gate is shown in Fig. 2.3a3. You will probably not be alone in asking what good the IDENTITY function is, as its output is always the same as its input. Frankly, the IDENTITY function serves no logical purpose. But, it is of real technical importance as a power amplifier. In pneumatics, power is determined as the product of flow times pressure. A low-power pilot-signal can control a high-power air-supply to the output.

The behaviour of the NC-valve, on the other hand, is fully documented in the events table of Fig. 2.3b2, and from this follows

$$y = 1 \Leftrightarrow x = 0,$$

$$Y \Leftrightarrow \overline{X},$$

16 2 Switching Devices

Fig. 2.4 Spool-and-sleeve valves as logic switches

The above function is called a NEGATION, the output always having the complementary value to the input.

The air supply of a spool-and-sleeve valve can be replaced by an input *signal*, as indicated in Fig. 2.4. The difference is that the air supply is *always* 1 while a signal can *vary*, meaning it can be either 0 or 1.

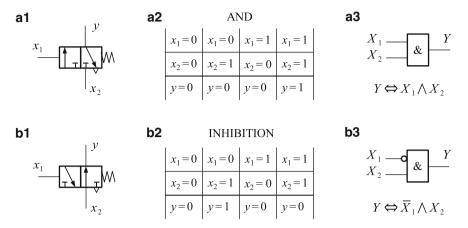

You will hopefully be able to recognise the valves' behaviour as being documented in the two event tables. The functions associated with these event tables are called AND and INHIBITION. The latter name stems from the fact that  $x_1$  *inhibits* y, meaning that, when  $x_1 = 1$ , the output y is blocked. It is probably routine to you by now to express the events tables of Fig. 2.4a2, b2 in the following formal manner:

$$y = 1 \Leftrightarrow x_1 = 1 \text{ AND } x_2 = 1,$$

$y = 1 \Leftrightarrow x_1 = 0 \text{ AND } x_2 = 1,$   $Y \Leftrightarrow X_1 \wedge X_2,$   $Y \Leftrightarrow \overline{X}_1 \wedge X_2.$

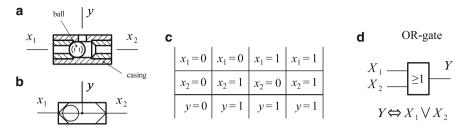

In the above usages the spool-and-sleeve valve cannot realise the logical OR function, a function no design engineer would like to do without. A cheap and effective realisation of the OR function is the shuttle valve of Fig. 2.5a. The ball in the design shown will always seal the input of lower pressure, connecting the output with the input of higher pressure. This valve is called a **passive** valve as the air of the output signal is derived from an input line, not from an air supply. This is a drawback, as is the fact that the valve does not have an exhaust of its own; the output must be exhausted via an input line. The standard symbol for this valve (Fig. 2.5b) is obviously inspired by the design shown in Fig. 2.5a. The events table describing the valve's behaviour marks the valve as a realisation of the OR function.

To see that the events table of Fig. 2.5c does describe the OR function, read the table row-wise (and not column-wise, as we have been doing up till now). First note that 'if  $x_1 = 1$  then y = 1' (this covering columns 2 and 3), and then that 'if  $x_2 = 1$

2.2 Electric Relays 17

Fig. 2.5 A shuttle valve to realise the OR function

Fig. 2.6 A valve realisation of a logic circuit

then y = 1' (which covers columns 1 and 3). Thus we reason that 'y = 1 iff  $x_1 = 1$  OR  $x_2 = 1$ ', and write this as

$$y = 1 \Leftrightarrow x_1 = 1 \text{ OR } x_2 = 1,$$

$Y \Leftrightarrow X_1 \lor X_2.$

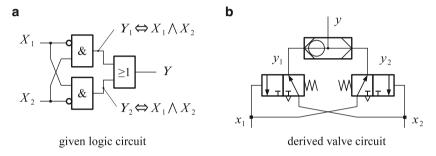

We are now in a good position to transform a given logic circuit into one consisting of valve symbols. Such a transition is shown in Fig. 2.6 for the running example of Chap. 1. Of course this example is only used to demonstrate a technique, and has nothing to do with the original problem of switching lights on or off. To replace the INHIBITIONs of Fig. 2.6a by NC-valves, note the correspondence laid down in Fig. 2.4.

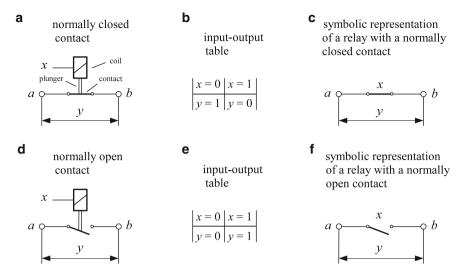

#### 2.2 Electric Relays

In its simplest form, an electric relay (see Fig. 2.7) consists of a coil, a plunger, and a contact that is actuated by the plunger. When currant flows through the coil its magnetic field attracts the plunger, thereby opening a *normally closed contact* (Fig. 2.7a) and closing a *normally open contact* (Fig. 2.7d). Interrupting the currant

18 2 Switching Devices

Fig. 2.7 The electric relay: principle operation, IO-table, symbol

to the coil allows a spring to return the plunger, and thus the contacts, to their initial positions.

The **input signal** to a relay is the voltage applied to the relay's coil, this voltage being represented by the binary variable  $x \in \{0, 1\}$  of Fig. 2.7. The **output signal**  $y \in \{0, 1\}$  stands for the **transmission** of the relay's contact, i.e., its ability to pass or transmit currant. The transmission y of a closed contact is taken to be 1, that of an open contact is 0.

Relays (as those of Fig. 2.7a, d) are *always* drawn under the assumption that their input signals are 0, i.e., that zero voltage is applied to their coils—this being referred to as the **normal state** of the relays. Thus, a *normally open contact*—a so-called NO-contact—is open (y=0) when the relay's coil is not energised (when x=0), and closed (y=1) when x=1. A *normally closed contact*—a NC-contact—is closed (y=1) when the relay's coil is not energised (x=0), and open (y=0) when x=1. This behaviour is expressed in the input-output tables (the events tables) of Fig. 2.7b, e. Stating when the outputs y of these tables are 1 is expressed formally in the logic formulas

$$y = 1 \Leftrightarrow x = 0,$$

$y = 1 \Leftrightarrow x = 1,$

$Y \Leftrightarrow \overline{X}.$   $Y \Leftrightarrow X,$

which show clearly that the relay with a normally closed contact is a NEGATION, while the relay with a normally open contact is an IDENTITY.

The **symbolic representation of a relay** (see Fig. 2.7c, f) consists of only two things: (a) a contact drawn in its *normal state*, its transmission y standing for the output of the relay, and (b) an input variable—in our example, x—which is the input

2.2 Electric Relays 19

signal to the coil activating the contact. The symbolic representation of a relay is an anachronism in that it has neither an input lead, nor a clearly defined output lead (such as the *logic symbols* of Sect. 1.5, or the *pneumatic symbols* of Sect. 2.1 have).

As stated for pneumatic valves, by **convention**, all relays in a circuit are drawn in their **normal state** which means that they are drawn as if their input signals were zero.

The coil of a relay usually activates multiple contacts, some normally open, the others normally closed. A single contact, or two or more interconnected contacts that transmit current to a *single load* comprise a **relay network**; for example, see the serial network of Fig. 2.8b or the parallel network of Fig. 2.9b. The interconnected contacts of a relay network are always drawn *in their normal state*, assigning to each contact the input variable of the coil activating it (in our cases, the variables x,  $x_1$ ,  $x_2$ , etc.). **The way the contacts are connected** unequivocally determines when the network's transmission y is 1. The network's transmission y is usually assigned to the network's load. A **load** is any device (such as a lamp, an electric motor, a relay coil, etc.) that receives and dissipates electric energy. The load is always needed to avoid the network from short circuiting. The only relay networks to be touched on here are the serial-parallel networks, well knowing that this does not do the possibilities of relay networks justice.

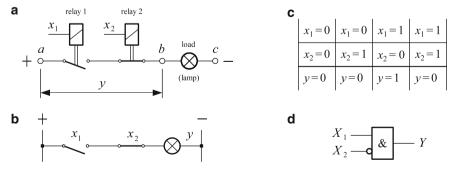

Figure 2.8a shows two relays in series, with a lamp as load. As explained in the above paragraph, the *relay network* is drawn as in Fig. 2.8b. The analysis of the input-output behaviour of Fig. 2.8a (or Fig. 2.8b, if you prefer) is undertaken in the events table of Fig. 2.8c, column 3 of this table stating when y is 1:

$$y = 1 \Leftrightarrow x_1 = 1 \text{ AND } x_2 = 0,$$

$Y \Leftrightarrow X_1 \wedge \overline{X}_2.$

This result lets us **conjecture** that the serial connection of two contacts is expressed by the logic AND ( $\land$ ), and that, vice versa, the logic AND ( $\land$ ) is realised by connecting two contacts in series. For our example, this conjecture allows us to

Fig. 2.8 Principle of a serial network

20 2 Switching Devices

Fig. 2.9 Principle of a parallel network

state that the behaviour of the circuits of the Figs. 2.8a, b is equivalent to that of the gate of sub-figure (d).

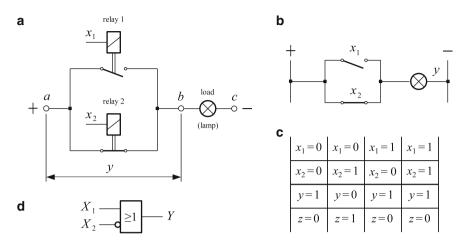

Figure 2.9a depicts relays connected in parallel, again with a lamp as a load; the symbolic relay network is drawn in Fig. 2.9b. From either of these representations we deduce that the circuit's transmission y is 1 when the transmission of at least one of the contacts is 1; this is expressed in the events table of sub-figure (c) when concentrating only on the transmission y (i.e., for the moment, not considering the variable z).

As with the shuttle valve of Fig. 2.5, we read the events table of Fig. 2.9c rowwise arguing that y = 1 iff  $x_1 = 1$  (hereby describing columns 3 and 4) OR  $x_2 = 0$  (which covers column 1 and again column 3),

$$y = 1 \Leftrightarrow x_1 = 1 \text{ OR } x_2 = 0,$$

$Y \Leftrightarrow X_1 \vee \overline{X}_2.$

This result lets us **conjecture** that the parallel connection of two contacts is expressed by the logic OR  $(\vee)$ , and that, vice versa, the logic OR  $(\vee)$  is realised by connecting two contacts in parallel. For the present example, this conjecture allows us to state that the behaviour of the circuits of the Fig. 2.9a, b is equivalent to that of the gate of sub-figure (d).

#### Inverting a Relay Circuit

There are two ways to invert a circuit. The simplest and most direct way is to invert the circuit's output. For instance, suppose we want to invert the circuit of

2.2 Electric Relays 21

Fig. 2.10 Expressing the OR-function using double negation

Fig. 2.9b. This is done by replacing the lamp—which is the circuit's output load—by an inverter, that is, by a normally closed relay as shown in Fig. 2.10a. The relay's coil, y, is now the load for the original circuit, while the lamp is the load, z, for the inverter. The values of z are shown in the bottom row of Fig. 2.9c—they are the complement of those for y.

The second way to invert a circuit is to calculate the inverted circuit directly from the inverted output z of Fig. 2.9c, obtaining

$$Z \Leftrightarrow \overline{X}_1 \wedge X_2$$

which leads to the circuit of Fig. 2.10b.

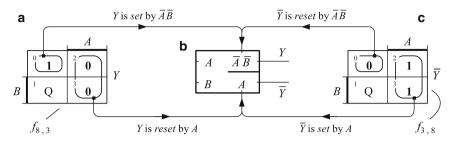

#### Realising Feedback

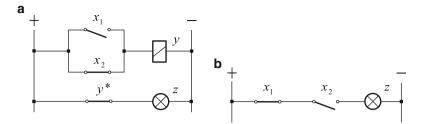

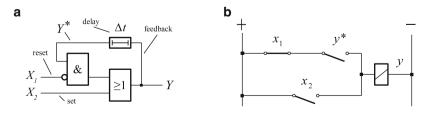

Feedback plays a dominating role in the design of so-called latches, these being elementary memory circuits. In fact they are so important that a whole Part of this book is devoted to them. In this early stage, we only want to see how to transform a logic feedback circuit, say, that of Fig. 2.11a, into a relay circuit. The output ORgate of sub-figure (a) requires our contact network to consist of two parallel paths, one of which contains the NO-contact  $x_2$ . The AND-gate of sub-figure (a) leads to the serial circuit consisting of the NC-contact  $x_1$  and the NO-contact named  $y^*$ . The load of the relay network is the coil y of a relay. To realise the *feedback* of the

Fig. 2.11 Transforming the logic circuit of a latch into a relay network

22 2 Switching Devices

latch pictured in sub-figure (a) we define the NO-contact  $y^*$  of sub-figure (b) to be actuated by the coil y.

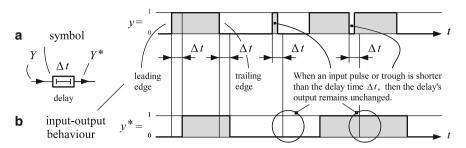

The delay  $\Delta t$  in the logic circuit of sub-figure (a) expresses the fact that the NO-contact  $y^*$  follows the coil's state of activation with the time delay of  $\Delta t$ . The logic circuit is thus modelled after the relay circuit. But it must be noted that the *theory* of feedback latches does not require the existence of a delay in the feedback loop.

#### 2.3 CMOS Transistors

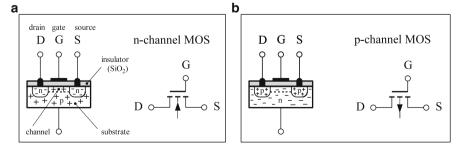

The transistor was invented in 1948 by John Bardeen, Walter Brattain and William Shockley and soon replaced the vacuum tube as a cheap amplifier. We shall take a look at only one transistor device, of a large proliferation, namely the CMOS technology. The transistors used are **insulated-gate field-effect transistors** (**IG-FET**)—Fig. 2.12—more commonly called **MOS** for the sequence of the layers of material used in their design—**metal-oxide-silicon**. There are two types of these transistors, according to the polarity (**n**egative or **positive**) of the electric charges used to create a conducting channel between the *drain* and the *source* regions: *n*-channel MOS (**NMOS**) and *p*-channel MOS (**PMOS**). Digital circuits that employ both these transistor types are called **complementary MOS** (**CMOS**), and have the advantage of needing only a single level of supply voltage.

For current to be able to flow between the drain and the source region, you need to *create a conducting channel* in the silicon between these regions. This is achieved by applying the proper voltage between the gate and the substrate. In an n-channel MOS you obtain a conducting channel by applying a more positive potential to the gate than to the substrate (the voltage from gate to substrate is positive), thus attracting negative charges to the gate while repulsing positive charges. In a p-channel MOS the conducting channel is obtained by making the voltage from substrate to gate positive, thus attracting positive charges to the gate while repulsing negative charges from the gate. *In actual usage, the source is always connected*

Fig. 2.12 Principle of the n-channel and p-channel MOS

2.3 CMOS Transistors 23

Fig. 2.13 The CMOS inverter

*to the substrate*. To obtain a channel, the density of source-type charges must be enhanced giving these transistors the name **enhancement type transistors**.

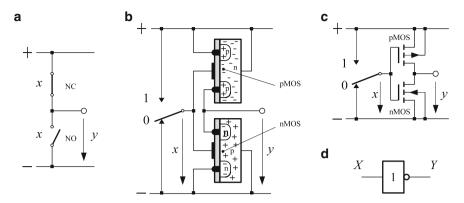

The simplest CMOS circuit is the **inverter** of Fig. 2.13. Its principle of operation is basic to CMOS technology. If you understand how the inverter works, you almost automatically understand the next two gates. The idea behind the inverter is shown in the relay circuit of Fig. 2.13a: The two serial contacts are always in a state of alternate transmission—when one is closed, the other is open. When the top switch, the NC-contact, is closed and the bottom switch, the NO-contact, open, the full supply voltage is fed through to the output *y*. *Vice versa*, the output *y* is zero when the top switch is open and the bottom one closed.

The relay circuit translates directly to the transistor circuit of Fig. 2.13b, the NC-contact being replaced by a PMOS, the NO-contact by an NMOS. In the circuit as drawn, the gates of both transistors are at ground potential dew to the way the switch governing the gate potential is set. As the substrate of the PMOS is connected to high potential a conducting p-channel is created. The NMOS transistor, on the other hand, is non-conducting as it has 0 voltage between gate and substrate, both being connected to ground. The voltage measurable at the output *y* is thus high. If the switch is brought to the alternate position, in which the potential at the gates of both transistors is high, the PMOS becomes non-conducting while the NMOS becomes conducting. The output voltage *y* is thus brought to zero. The actual circuit, of course, is always drawn using MOS symbols, giving you Fig. 2.13c. As the input and output of this circuit are always complementary, it is an inverter or a negation, the symbol for which is shown in Fig. 2.13d.

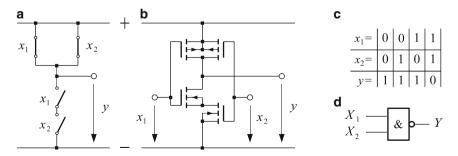

There are two successful ways, of four trivial ones, to generalise the principle inverter circuit of Fig. 2.13a: One of these is shown in Fig. 2.14a, the other in Fig. 2.15a, and both lead to circuits superbly adapted to CMOS technology.

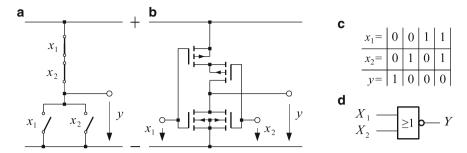

The first generalisation of the inverter of Fig. 2.13a is achieved by substituting the single NC-contact by two serial NC-contacts, and substituting the single NO-contact by two parallel NO-contacts—this leading to Fig. 2.14a. The equivalent

24 2 Switching Devices

Fig. 2.14 The CMOS NOR-circuit

CMOS circuit is obtained by substituting PMOS transistors for NC-contacts, and NMOS transistors for NO-contacts. As with the inverter of Fig. 2.13c, note that in Fig. 2.14b the sources and substrates of the PMOS transistors are connected to high potential, or at least higher potential, while the sources and substrates of the NMOS transistors are connected to low (or lower) potential.

The simplest way to analyse the circuit of Fig. 2.14 is to develop the events table shown in Fig. 2.14c. You start out with the table of input events, leaving the bottom row, the one for the output y, empty. Then, for each input event, you deduce from the behaviour of the circuit the value for the output y, entering the outputs into the bottom row. Considering the result, you will notice that inverting each output value leads to the **or** function. In other words, the events table of Fig. 2.14c is that of a **not-or** function, usually referred to as the **nor** function. The logic symbol used for this function is shown in Fig. 2.14d; it is simply an OR gate with an inverted output.

The second generalisation of the inverter leads to Fig. 2.15a and that to Fig. 2.15b. The analysis needed to obtain the events table of Fig. 2.15c is easy so that I again leave the details to you. The result, as you will have noticed, is the inversion of the **and** function, i.e. is a **not-and** function, and is thus referred to as the **nand** function, the logic symbol for which is shown in Fig. 2.15d.

Fig. 2.15 The CMOS NAND-circuit

2.3 CMOS Transistors 25

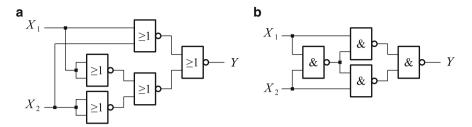

Fig. 2.16 NOR and NAND versions of our running example

Of course the CMOS circuits discussed here are only a small excerpt of the circuits used. But they are basic and absolutely essential to the understanding of the techniques employed. One of the most important omissions is a discussion of circuits with feedback, circuits that lead to the realisation of memory devices—so-called *latches* and *flip-flops*. These circuits are discussed, together with their theory, in later chapters.

The logic building blocks of CMOS technology are NAND-, NOR- and NEGATION-gates. These, therefore, one wishes to use when realising logic circuits in CMOS technology. To get an impression of pure NOR- and NAND-design, take a look at Fig. 2.16. These circuits are equivalent to that of Fig. 1.5 of our running example of Chap. 1. Transforming larger AND, OR and NOT based circuits into NOR or NAND circuits can be quite demanding and is discussed in a later chapter.

# **Chapter 3 Elementary Logic Functions**

Elementary logic functions are the building blocks of all logic functions however complicated they may be, and are thus of prime importance. In the following pages we discuss all elementary logic functions and how they interact. Much of this material, such as the summaries of theorems, is only intended as reference to be at hand when needed (e.g., in calculations, or for theoretical considerations).

# 3.1 Logic Functions

An **elementary logic function** F maps a pair of ordered *truth values*, FALSITY (for which we write  $\mathbf{0}$ ) and TRUTH (denoted as  $\mathbf{1}$ ), into the set  $\{\mathbf{0}, \mathbf{1}\}$  of truth values

$$F: \{\mathbf{0}, \mathbf{1}\}^2 \mapsto \{\mathbf{0}, \mathbf{1}\}$$

These functions have, at most, two input variables and are summarised in the table of Fig. 3.1. The middle column of this table shows function symbols commonly used in switching algebra. These function symbols— $\land$ ,  $\gt$ ,  $\lt$ ,  $\Leftrightarrow$ ,  $\lor$ ,  $\lor$ ,  $\hookleftarrow$ ,  $\leftrightarrow$ ,  $\rightarrow$ ,  $\stackrel{\sim}{\land}$ ;  $\neg$ —are called **logic connectives**. Those that take two arguments are **dyadic logic connectives**. The only one that takes a single argument, the NEGATION symbol  $\neg$ , is referred to as a **monadic logic connective**.

Actually, the symbols > and < for the INHIBITIONs,  $\overset{\sim}{\vee}$  for NOR, and  $\overset{\sim}{\wedge}$  for NAND are not common—these symbols were introduced by **Iverson** for APL. Iverson's notation for the INHIBITIONs was chosen because it is mnemonic and because there is no generally accepted notation for these functions. In the case of NOR and NAND Iverson's notation is mnemonically clearly superior to the respective notations of **Sheffer**  $(X_1 \downarrow X_2 : \Leftrightarrow X_1 \overset{\sim}{\vee} X_2)$  and **Nicod**  $(X_1|X_2 : \Leftrightarrow X_1 \overset{\sim}{\wedge} X_2)$  sometimes used. In switching algebra the negation of a variable X is commonly denoted as  $\overline{X}$  whereas in logic the negation would preferably be written as  $\neg X$ .

| Definition                          | Logic                                                   | Name of the              |

|-------------------------------------|---------------------------------------------------------|--------------------------|

| $X_1 \leftrightarrow 0 \ 0 \ 1 \ 1$ | notation                                                | logic                    |

| $X_2 \leftrightarrow 0 1 0 1$       |                                                         | function                 |

| $Y_0 \leftrightarrow 0 \ 0 \ 0 \ 0$ | $Y_0 \Leftrightarrow 0$                                 | CONTRADICTION, FALSITY   |

| $Y_1 \leftrightarrow 0 \ 0 \ 0 \ 1$ | $Y_1 \Leftrightarrow X_1 \wedge X_2$                    | CONJUNCTION, AND         |

| $Y_2 \leftrightarrow 0 \ 0 \ 1 \ 0$ | $Y_2 \Leftrightarrow X_1 > X_2$                         | INHIBITION               |

| $Y_3 \leftrightarrow 0 \ 0 \ 1 \ 1$ | $Y_3 \Leftrightarrow X_1$                               | IDENTITY                 |

| $Y_4 \leftrightarrow 0 \ 1 \ 0 \ 0$ | $Y_4 \Leftrightarrow X_1 < X_2$                         | (transposed) INHIBITION  |

| $Y_5 \leftrightarrow 0 1 0 1$       | $Y_5 \Leftrightarrow X_2$                               | IDENTITY                 |

| $Y_6 \leftrightarrow 0 1 1 0$       | $Y_6 \Leftrightarrow X_1 \oplus X_2$                    | ANTIVALENCE, XOR         |

| $Y_7 \leftrightarrow 0 1 1 1$       | $Y_7 \Leftrightarrow X_1 \vee X_2$                      | DISJUNCTION, OR          |

| $Y_8 \leftrightarrow 10000$         | $Y_8 \Leftrightarrow X_1 \overset{\sim}{\vee} X_2$      | NOR, Sheffer function    |

| $Y_9 \leftrightarrow 1001$          | $Y_9 \Leftrightarrow X_1 \leftrightarrow X_2$           | (material) EQUIVALENCE   |

| $Y_{10} \leftrightarrow 1010$       | $Y_{10} \Leftrightarrow \overline{X}_2$                 | NEGATION, NOT            |

| $Y_{11} \leftrightarrow 1011$       | $Y_{11} \Leftrightarrow X_1 \leftarrow X_2$             | (transposed) IMPLICATION |

| $Y_{12} \leftrightarrow 1 1 0 0$    | $Y_{12} \Leftrightarrow \overline{X}_1$                 | NEGATION, NOT            |

| $Y_{13} \leftrightarrow 1 1 0 1$    | $Y_{13} \Leftrightarrow X_1 \to X_2$                    | (material) IMPLICATION   |

| $Y_{14} \leftrightarrow 1110$       | $Y_{14} \Leftrightarrow X_1 \overset{\sim}{\wedge} X_2$ | NAND, Nicod function     |

| $Y_{15} \leftrightarrow 1111$       | $Y_{15} \Leftrightarrow 1$                              | TAUTOLOGY, TRUTH         |

Fig. 3.1 Table of the elementary logic-functions

Happily, it suffices to use sub-sets of the set of elementary connectives,  $\{\neg, \land, >, <, \oplus, \lor, \overset{\smile}{\lor}, \longleftrightarrow, \overset{\smile}{\leftarrow}, \overset{\smile}{\rightarrow}, \overset{\smile}{\land}\}$ , to be able to write the logic expression of a general logic function. These *sets of necessary and sufficient connectives* are frequently referred to as **functionally complete sets** (of connectives). They are compiled in the leftmost and rightmost columns of Fig. 3.2. Without proof at this point, let it be said that all general functions can be realised with the AND, OR, and NOT

| set                       | $\neg A \Leftrightarrow$     | $A \wedge B \Leftrightarrow$                                                          | $A \lor B \Leftrightarrow$                                                         | dual set                        |

|---------------------------|------------------------------|---------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|---------------------------------|

| $\{\widetilde{\wedge}\}$  | $A\stackrel{\sim}{\wedge} A$ | $(A \stackrel{\sim}{\wedge} B) \stackrel{\sim}{\wedge} (A \stackrel{\sim}{\wedge} B)$ | $(A \overset{\sim}{\wedge} A) \overset{\sim}{\wedge} (B \overset{\sim}{\wedge} B)$ | $\{\widetilde{\vee}\}$          |

| $\{\land, \lnot\}$        | $\neg A$                     | $A \wedge B$                                                                          | $\neg(\neg A \land \neg B)$                                                        | {∨, ¬}                          |

| $\{ ightarrow, 0\}$       | $A \rightarrow 0$            | $(A \to (B \to 0)) \to 0$                                                             | $(A \to B) \to B$                                                                  | {>, 1}                          |

| $\{ \rightarrow, \neg \}$ | $\neg A$                     | $\neg (A \rightarrow \neg B)$                                                         | $\neg A \rightarrow B$                                                             | {>, ¬}                          |

| $\{\oplus, \wedge, 1\}$   | $A \oplus 1$                 | $A \wedge B$                                                                          | $A \oplus B \oplus (A \wedge B)$                                                   | $\{\leftrightarrow,\lor,0\}$    |

| $\{\oplus,\vee,1\}$       | $A \oplus 1$                 | $A \oplus B \oplus (A \vee B)$                                                        | $A \vee B$                                                                         | $\{\leftrightarrow, \land, 0\}$ |

Fig. 3.2 Functionally complete sets of connectives

Fig. 3.3 Dual connectives

functions, i.e.,  $\{\land, \lor, \neg\}$  is a functionally complete set. The formulas in the three central columns of a given row state how to realise the functions NOT, AND, and OR using the connectives stated in the functionally complete set of the leftmost column. The functionally complete sets in the rightmost column are **dual** to the sets in the leftmost column. This refers to the fact that replacing truth values and connectives by their duals, according to Fig. 3.3, transforms one correct formula into another one which is then also correct. The formulas are called (mutually) dual.

The sequence in which the logic connectives are acted upon in a given formula is determined solely by parentheses. But this causes their number to grow quite rapidly for lengthy formulas. To counteract this, one uses a *convention of adhesion* that introduces an artificial priority at least between the most commonly used logical connectives.

**Convention of adhesion:** A given connective of  $(\neg, \land, \lor, \rightarrow, \leftrightarrow)$  has a stronger adhesion to its arguments than any connective of the quintuple listed to its right. In other words, any connectives listed to the left of another is acted upon before acting upon this other one.

This convention allows us to rewrite the following formula in the indicated ways:

$$((A \land B) \lor ((\neg A) \land B)) \leftrightarrow B \Leftrightarrow$$

$$(A \land B) \lor (\neg A \land B) \leftrightarrow B \Leftrightarrow$$

$$A \land B \lor \neg A \land B \leftrightarrow B$$

When  $\wedge$ - and  $\vee$ -connectives occur alternatively, one is prone to confuse them. It is thus common to adhere to the

**Convention of omitting the \land-connective:** One may write PQ instead of  $P \land Q$  when it seems appropriate.

The last of the previous formulas may then be written  $AB \lor \neg AB \leftrightarrow B$  which is quite easy to read, as you will hopefully agree. In contrast to the above procedure, it is sometimes advantageous not to **bind** arguments to (dyadic) connectives but to **separate** the arguments from the connectives. This is done in the

**Convention of separation:** *Dots* attached to dyadic connectives (as in  $. \wedge ., :\leftrightarrow :, .:\rightarrow :.$ ) separate these from their arguments. The more dots, the stronger the separation. But, for two different kinds of connectives, both with the same number of dots, the above *convention of adhesion* prevails.

The following example of the application of the *convention of separation* demonstrates that the dots need not occur symmetrically.

$$(A \to (B \to C)) \to (A \land B \to C) \Leftrightarrow$$

$$A \to (B \to C) \to A \land B \to C \Leftrightarrow$$

$$A \to B \to C \to A \land B \to C$$

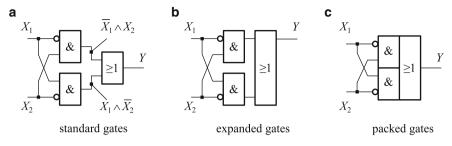

#### 3.2 Basic Gates

A gate is a specific graphic symbol for a logic function. As such, it expresses an idealised behaviour of a switching device. Viewing it the other way around, the behaviour of a real-world switching device is an approximation of a gate's behaviour. Gates were preliminarily introduced in Sect. 1.5 especially stating how to connect them to express a given logic formula. Not every logic function has a gate assigned to it. Those gates that do exist are called **basic**, hereby emphasising that all other logic functions are represented by graphic symbols comprised of basic gates. A basic gate is given the same name as the function it represents. If a gate has one input it is called **monadic**, if it is has two inputs it is called **dyadic**.

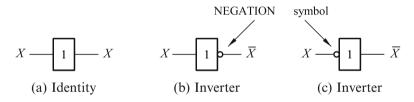

Fig. 3.4 The monadic gates. (a) Identity (b) Inverter (c) Inverter

There are two logic functions with a single input, the IDENTITY and the NEGATION. The IDENTITY gate, shown in Fig. 3.4a, is a rectangle with a 1 written into it. A gate representing a NEGATION is an IDENTITY gate with either the input or output signal marked by a small circle representing inversion and drawn where a lead enters or leaves the rectangle, see Fig. 3.4b, c.

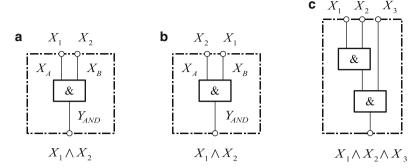

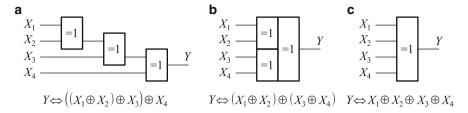

Only four basic dyadic gates exist, called AND, OR, XOR, and EQUIVA-LENCE, (Fig. 3.5), each representing the equally named logic functions. But, why

Fig. 3.5 The dyadic gates

3.2 Basic Gates 31

Fig. 3.6 On commutativity and associativity

are gates only defined for these four functions? For a gate to be of practical use, it must represent a function that is **associative** and **commutative**, and only the above mentioned functions have both these properties as discussed further on. As for the rather curious choice of inscriptions (&,  $\ge 1$ , =1, =) distinguishing the gates, I'm afraid you'll just have to accept them—they are international standard as declared by the International Electrotechnical Commission (IEC 117-15).

**Commutativity** allows you to interchange the input signals to a gate as you like without being able to notice a change in the behaviour of the output value. For instance, assigning  $(X_1, X_2)$  to  $(X_A, X_B)$  in Fig. 3.6a will give the same result as assigning  $(X_2, X_1)$  to  $(X_A, X_B)$  in Fig. 3.6b.

**Associativity** permits you to *cascade* identical gate types thus creating a multiple-input gate of that type. For instance, cascading two dual-input AND-gates, as shown in Fig. 3.6c, leads to a triple-input AND-gate. Its inputs are again commutative and associative.

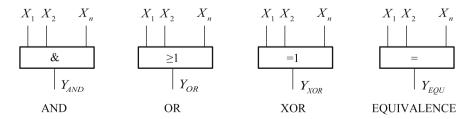

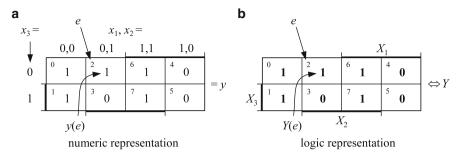

Due to the properties of commutativity and associativity, the four dyadic functions AND, OR, XOR, and EQUIVALENCE can be used to create gates with multiple inputs as shown in Fig. 3.7.

The output variables for these multiple-input gates can be stated quite strait forwardly as

Fig. 3.7 Gates with multiple inputs

$$Y_{AND} \Leftrightarrow X_1 \wedge X_2 \wedge \cdots \wedge X_n,$$

$Y_{XOR} \Leftrightarrow X_1 \oplus X_2 \oplus \cdots \oplus X_n,$   $Y_{OR} \Leftrightarrow X_1 \vee X_2 \vee \cdots \vee X_n,$   $Y_{EOU} \Leftrightarrow X_1 \leftrightarrow X_2 \leftrightarrow \cdots \leftrightarrow X_n,$

You might like to try to formulate when the output values of these functions are 1. This is quite easy for AND and OR, but before continuing try to state when the outputs of the multiple XOR and multiple EQUIVALENCE are 1.

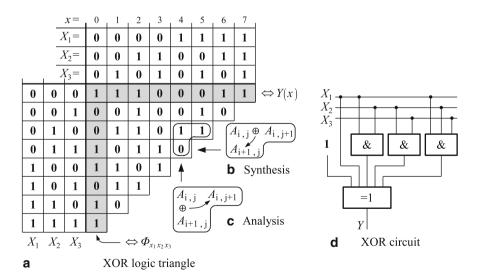

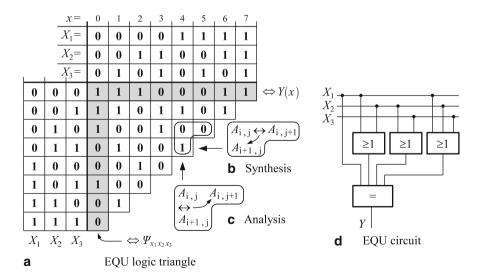

A summary of when these functions are 1 is given in the following statements.

```

AND: Y_{AND} is 1 iff all inputs are 1.

OR: Y_{OR} is 1 iff at least one input is 1.

XOR: Y_{XOR} is 1 iff an odd number of the inputs are 1.

EQU: For an even number of inputs (greater than or equal to 2):

Y_{EQU} is 1 iff an even number of the inputs are 1

(0 is taken as even).

For an odd number of inputs:

Y_{EQU} is 1 iff an odd number of the inputs are 1.

```

The above statements are illustrated in the tables of Fig. 3.8 for three and for four input variables. You will possibly want to compare the rows for  $Y_{XOR}$  and  $Y_{EQU}$  more carefully. There is one case which tends to cause confusion in the definition stating when the output of the EQUIVALENCE function is 1: Given an *even* number of inputs, why is the output 1 when all inputs are  $\mathbf{0}$ ?

Saying that 'No inputs are 1' is the same as saying 'Zero inputs are 1' so that the output is 1 because an even number (albeit that this number is zero) of inputs are 1.

From the above statements, saying when XOR and EQUIVALENCE are 1, we deduce that their outputs are inverted for functions with an even number of input variables, and are logically equivalent for functions with an odd number of input variables:

```

Y_{EQU} \Leftrightarrow \overline{Y}_{XOR} for an even number of inputs,

Y_{EOU} \Leftrightarrow Y_{XOR} for an odd number of inputs.

```

Fig. 3.8 AND, OR, XOR and EQUIVALENCE for three and four inputs

Fig. 3.9 The four derived gates

This rather inconsistent behaviour of  $Y_{EQU}$  usually lets us work with the XOR function instead of the EQUIVALENCE function.

The functions INHIBITION, IMPLICATION, NOR, and NAND can be represented by AND, OR and NOT leading to the gate representations of Fig. 3.9.

# 3.3 Using AND, OR and NOT

The most common functionally complete set of connectives is  $\{\land, \lor, \neg\}$ , i.e., the set of AND, OR, and NOT functions and gates. When using these functions it is useful to summarise the relevant theorems, e.g., as is done in the table of Fig. 3.10. None of these theorems, nor those following in this chapter, are proven in this text.

| Basic theorems on negation                                                                                                                 |                                                                        |  |

|--------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|--|

| $\bar{0} \Leftrightarrow 1$                                                                                                                | $\bar{1} \Leftrightarrow 0$                                            |  |

| $\overline{\overline{A}} \leftarrow$                                                                                                       | $\Rightarrow A$                                                        |  |

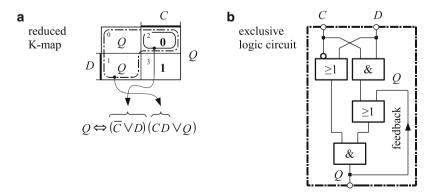

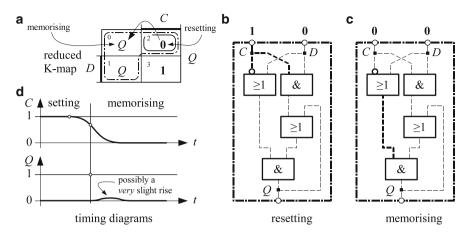

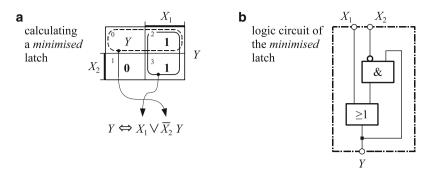

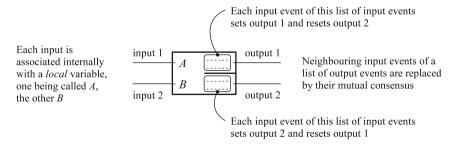

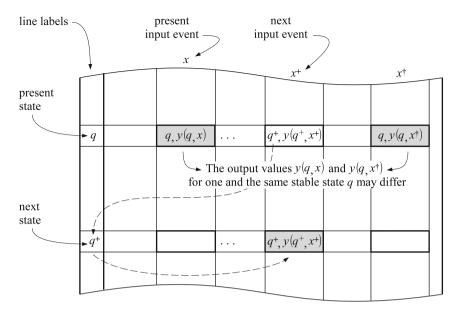

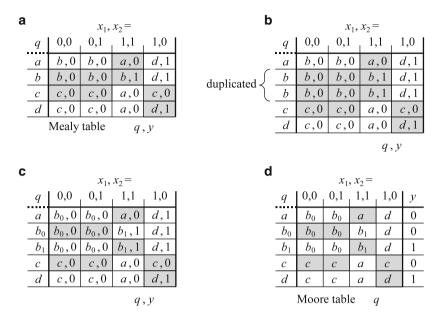

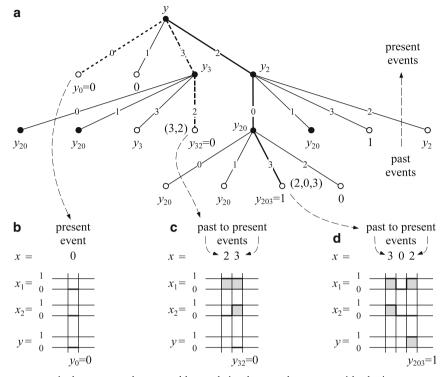

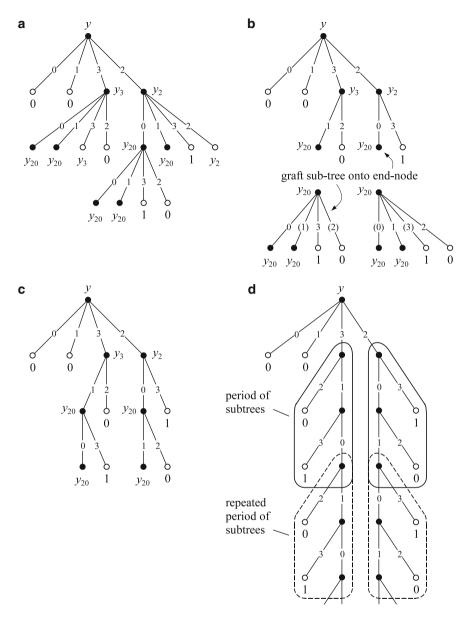

| DeMorgan                                                                                                                                   | 's theorems                                                            |  |